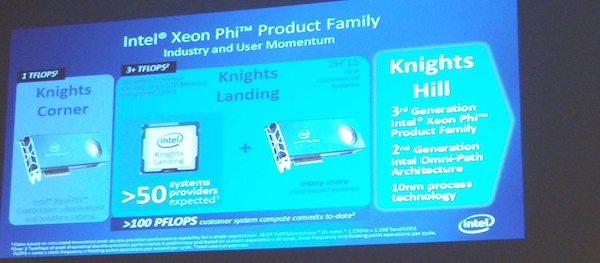

【美國奧勒岡州現場報導】英特爾為超級電腦和HPC伺服器打造的超多核心協同處理器Xeon Phi將推出第二代產品,英特爾今日( 3/24)揭露更多關於代號Knights Landing的第二代Xeon Phi超多核心協同處理器細節,並透露將在今年下半年率先推出3款Knights Landing超多核心處理器版本,包括提供了1款標準型,以及2款高階伺服器級別的處理器產品。

英特爾表示,將推出的3款Knights Landing產品,分別是KNL Coprocessor處理器、Host Processor處理器,以及Host Processor with Integrated Fabric處理器三種不同版本,三款處理器皆擁有超過60顆以上的核心,其運算效能也都突破3 TFLOPS的運算能力,並可獲得與DDR4相比至少5倍的記憶體頻寬提升。

i

i

英特爾指出,這3款Knights Landing超多核心處理器產品當中,Host Processor與Host Processor with Integrated Fabric處理器,主要專門用來滿足伺服器彈性擴充的需求,因此,在記憶體容量上最高可支援384GB容量,同時,兩款的功耗也比標準型的KNL Coprocessor處理器,獲得了超過2成(25%)的能耗改善,而在I/O方面,也提供Host Processor with Integrated Fabric版本支援光纖整合介面,至於Host Processor與KNL Coprocessor處理器則分別採用了光纖與PCle介面。

預計首款搭載Knights Landing處理器的商業系統,將在2015年下半年問世。英特爾也表示,屆時也將有超過50家供應商推出搭載Knights Landing處理器的系統。

Xeon Phi採用了專為超級電腦和高效能運算打造的超多核心架構(Many Integrated Core,MIC)設計,英特爾在2010年先發表了代號為Knights Corner的第一代產品,2013年6月也發表使用14奈米製程,代號Knights Landing的第二代產品。

不同於第一代的Knights Corner,新的Knights Landing核心架構,採用了超過60個Silvermont架構核心,不只在處理器整體運算效能上可達到3 TFLOPS的運算能力,單執行緒效能也比起現有Knights Corner架構快上3倍。

此外,Knights Landing處理器內建了16GB高速記憶體,其頻寬幾乎達到了DDR4的5倍,同時採用6通道記憶體技術,最大可支援384GB DDR4記憶體容量。該處理器也是第一個整合Omni Scale Fabric高速光纖的Xeon Phi產品系列,用來提升整體系統的效能,而在I/O方面,Knights Landing也能支援最多36通道的PCIe 3.0介面。

英特爾現場也實際展示了第二代Knights Landing架構的Xeon Phi超多核心協同處理器晶片,不過該展示處理器尚未包含Omni-Path架構。

新的Knights Landing架構超多核心協同處理器,擁有超過60個Silvermont架構核心,採用14奈米製程,共超過有80億顆電晶體。

英特爾工作站與高效能運算資料中心事業群產業發展暨行銷總監Hugo Saleh表示,高效能運算(HPC)歷經從使用於物理現象的挖掘,到後來,運用在大量資料模擬驗證的大資料分析上,衍然已成為一種用來轉換與驅動資料的科學,而現在,更走向了提供公有雲及私有雲服務做為高效能運算的應用。他也說,像是透過HPC的即時分析技術,可從每秒將近300萬筆的交易資料中找到最佳關聯性,提供企業做更有效的交易管理與應用。

Saleh表示,未來HPC應用將逐步從使用者為主,走向以提供服務為主的HPC服務邁進。像是建立一個基於雲端的HPC平臺,未來只需透過API介接就能提供消費者或企業各式HPC應用及服務,並依照需求提出不同客製化解決方案,如,針對具高度運算需求的用戶提供高階運算服務等,也可做為企業打造私有雲的HPC服務。

他也認為,HPC的下一個舞臺將會擁抱開源碼、開放資料,以及開放創新,以此來建立新的商業模式,並也提供運用於高效能運算的3D印表機上使用。除了Knights Landing以外,英特爾也在去年底公布了代號為Knights Hill的第三代 Xeon Phi超級電腦核心架構藍圖,首度採用10奈米製程與第二代的Omni-Path架構技術。

熱門新聞

2026-02-09

2026-02-10

2026-02-06

2026-02-09

2026-02-10

2026-02-09

2026-02-10