【NetApp AFF A400的卸載引擎卡】NetApp新推出的中階全快閃儲存陣列AFF A400,在控制器的PCIe 3插槽中,預載了1張基於ASIC的卸載引擎卡(offload engine card),含有2個用於A400雙控制器互連的100GbE埠,以及用於壓縮與重複資料刪除的硬體運算功能。(圖片來源/NetApp)

企業儲存正加速邁向硬體加速時代,我們在9月份的儲存月報《企業儲存的硬體加速時代來臨》中,才介紹了當前企業儲存設備導入硬體加速功能的情況,短短3個多月來,企業儲存硬體加速的應用又出現許多新變化,有了更多樣化的發展。

首先,是應用的產品範圍,從早先的高階儲存陣列,擴展到中階儲存陣列。

其次,是硬體加速裝置的架構,從先前的ASIC開始轉往FPGA。

儲存硬體加速的基本型式

為儲存設備引進加速用硬體,是對「軟體定義化」風潮的一個「反動」 ,面對日趨複雜的I/O處理需求,特別是即時壓縮、重複資料刪除等應用帶來的繁重資料縮減運算需求,純粹依靠通用處理器硬體的軟體定義化架構,已逐漸不勝負荷。

而透過專用硬體晶片來處理RAID Parity計算,以及壓縮、解壓縮,重複資料刪除特徵值比對等固定運算,要比控制器的通用型處理器更具效率,因而可減輕儲存控制器的負擔,達到改善儲存設備整體效能的目的。

依照儲存設備搭載加速硬體的型式,儲存加速硬體的架構,又可分為結合在控制器核心的專用加速晶片,或是透過附加模組提供的硬體加速卡兩大類,前者內嵌於控制器核心內,後者則是附加的板卡或模組。

而依照卸載運算的型式,儲存設備的加速硬體又分為卸載I/O處理,以及卸載資料縮減運算兩大類型,前者如RAID Parity運算、控制器內部互連存取控制與管理等,後者則包括壓縮、解壓縮,以及重複資料刪除特徵值比對等。

中階儲存設備的硬體加速

額外的硬體晶片,意味著額外的硬體成本,所以專用加速硬體過去多是應用在對效能敏感、對成本則相對較不敏感的高階儲存陣列上。不過到了今日,開始有一些新推出的中階儲存陣列產品,也導入了加速用硬體,例如NetApp不久前發表的AFF A400全快閃儲存設備,便是其中的代表性產品。

在此之前,只有HPE 3PAR StoreServ等極少數堅持「通用處理器+ASIC」架構的產品線,在中階產品提供ASIC加速硬體,而NetApp則在AFF系列中,開啟了中階產品引進ASIC加速的新範例。

A400是NetApp AFF全快閃儲存陣列家族的中階產品新成員,替代了上一代的A300,從機箱、硬體核心到I/O介面都有更新,特別的是,A400的控制器預載了1張基於ASIC的卸載引擎卡(offload engine card),這張卡含有2個100GbE埠,用於A400雙控制器之間互連,還擁有硬體運算功能,可用於壓縮、解壓縮與重複資料刪除特徵值運算比對等,藉此為處理器卸載運算負擔。

FPGA接替ASIC的硬體加速架構

在10多年以前,通用處理器+ASIC晶片曾是儲存陣列控制器的標準核心運算架構,由ASIC作為通用處理器的輔助,但由於ASIC開發成本高昂,也導致儲存廠商逐漸放棄ASIC,改以CPU加上軟體處理作為替代。不過FPGA技術的出現,提供了一種成本較ASIC更低的專用加速硬體型式。

例如HPE的SimpliVity產品線,便採用了基於Xilinx FPGA晶片的加速卡,用於搭配其儲存軟體平臺,提供壓縮與重複資料刪除運算功能。而在Hitachi Vantara新推出的旗艦機型VSP 5000上,更清楚展現了FPGA取代ASIC的趨勢。

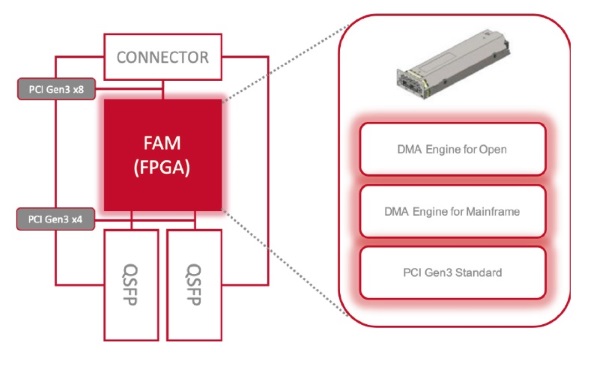

眾所皆知,Hitachi Vantara是非常硬體處理導向的日系儲存大廠,如上一代的旗艦機型VSP F1500/G1500,便透過ASIC,來處理包括大型主機I/O處理與控制器互連傳輸在內的許多工作負載。而在新一代的VSP 5000上,則改以SVOS儲存作業系統軟體功能,來處理大型主機相關的I/O處理作業,同時,也導入內含FPGA晶片的FAM模組(Fabric Accelerated Module),來作為控制器內部互連網路的中介,卸載控制器互連的I/O處理負擔。

每組VSP 5000的控制器可安裝2組FAM模組,每組FAM模組含有2個埠,透過4條PCIe 3鏈路與互連交換器(Interconnect Switch)連接,然後再與其他控制器連結。

在沒有FAM模組時,面對跨控制器之間的資料傳輸時,目標端控制器的處理器,除了應付處理來源端控制器發出的資料傳輸指令要求,也必須處理資料傳輸作業,從而耗費許多處理器週期。而在有了FAM模組後,改由這些模組來處理資料傳輸指令,並直接存取控制器記憶體,然後回覆給來源端控制器,藉此卸除了目標端控制器的相關處理負擔。

Hitachi Vantara宣稱,透過FAM模組提供的I/O卸載功能,可以為VSP 5000提供多達46%的IOPS效能提升,而這項技術,也是VSP 5000之所以能提供當前業界最高的2,100萬IOPS效能,同時保有70μs的低存取延遲關鍵所在。

【Hitachi Vantara VSP 5000的FAM加速模組】VSP 5000每組控制器,可以安裝2組基於FPGA的FAM模組(Fabric Accelerated Module),用於處理控制器之間的互連資料傳輸作業,藉此卸載處理器的運算負擔,進而顯著提高整體的I/O效能。(圖片來源/Hitachi Vantara)

儲存硬體架構的螺旋式發展

隨著專用加速硬體在儲存應用上的逐漸擴展,也讓儲存陣列的硬體架構演進,出現了螺旋式的發展。

在2000年代初期時,儲存陣列控制器核心普遍採取的運算組態,是通用處理器+專屬ASIC晶片的架構,通用處理器負責一般管理,ASIC則承擔I/O處理作業。但由於ASIC開發成本高昂,當通用處理器功能與效能逐漸提高後,便開始轉往完全依靠通用處理器的架構。

沿著這個發展趨勢,接下來不僅控制器核心走向通用硬體架構,包括整個儲存陣列系統,都開始以標準的通用伺服器硬體構成,從而抹除了儲存陣列與伺服器的界線,只剩下運行軟體的區別,形成了儲存設備的「軟體定義化」。

不過這幾年來,情況又有了改變,隨著壓縮與重複資料刪除等技術,逐漸成為當前市面上儲存陣列基本功能,也導致儲存陣列控制器的運算壓力急驟增加,因而一些對效能敏感的高階儲存陣列與全快閃儲存陣列,開始導入專用硬體,來為處理器卸載這些運算,這也讓儲存陣列的核心架構,再次回到十多年前的「通用處理器+專屬晶片」的混合架構,但區別在於,現在儲存陣列導入專屬晶片的目的,是以卸載資料縮減運算為主。此外,專用晶片的型式也從過去的ASIC,開始轉向FPGA。

熱門新聞

2026-02-09

2026-02-06

2026-02-06

2026-02-06

2026-02-06

2026-02-06