iThome

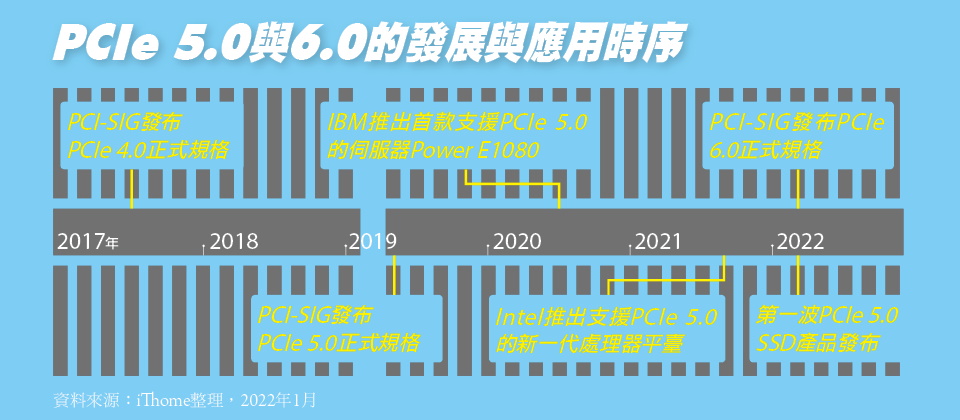

當PCI-SIG於2017年中發布PCIe 4.0規格時,曾表示他們接下來會加速制定規格的腳步,以彌補先前延宕的時光。該小組確實兌現承諾,在PCIe 4.0問世後不過4年半時間,便接連發布PCIe 5.0與6.0等2個世代的新規格。

目前PCIe 5.0正以超乎尋常的速度進入市場,正式規格發布不過2年時間,應用環境便已初步就緒,於2021年底到2022年初,湧現了第1批支援PCIe 5.0的電腦平臺與周邊裝置產品。

至於2周前剛剛發布正式規格的PCIe 6.0,則是自PCIe 3.0以來,PCIe發展歷程中最大的一次技術變革,引進新的編碼技術,以實現提高傳輸速率的目標。

迅速推進的PCIe 5.0產品

PCIe 5.0的架構與PCIe 4.0相似,同樣採用128b/130b編碼技術,但每通道(lane)的傳輸速率提高到32 GT/s,是PCIe 4.0的2倍,更是PCIe 3.0的4倍,同時仍保有向下相容性。

在匯聚16條通道的x16組態下,PCIe 5.0可提供128Gb/s的總頻寬,足以支撐新一代400GbE資料中心骨幹網路的需求,也能為不同周邊裝置的傳輸應用,在成本與頻寬之間取得更佳的平衡。

一開始,PCIe 5.0的應用進度也和前幾代PCIe相近,自PCI-SIG於2019年5月發布規格後,Rambus、Microchip等元件廠商,便於2019年底到2020年初陸續推出相關的控制元件。如同PCIe 4.0剛發布時的情況,IBM也是第一波應用PCIe 5.0的大廠,在2020年8月宣布Power 10處理器平臺將納入PCIe 5.0,接著在一年後的2021年9月,推出基於Power 10的Power E1080伺服器,成為最早支援PCIe 5.0的主機產品。但Power 10這種專屬平臺,不足以成為推動PCIe 5.0應用的力量。

到此時為止,PCIe 5.0的應用進程,都和先前歷代PCIe相似,依照過去的經驗,下一步的應用進程,應該是在2021年底到2022年初之間,出現第一批採用PCIe 5.0的SSD等周邊裝置產品,然後在2022年下半年到2023年初左右,開始進入主流的x86平臺電腦與伺服器應用。

如同預期,第一批支援PCIe 5.0的SSD產品在2022年初的CES大會中湧現,除此之外,PCIe 5.0的應用也擴展到高階網路卡領域,例如Nvida的400Gb高階網路卡與資料處理器卡(DPU),都是基於PCIe 5.0介面。

但出人意料的是,或許是記取了先前在PCIe 4.0時期,落後於競爭對手AMD的教訓,在前述PCIe 5.0周邊裝置發表之前,Intel搶先在2021年10月宣布,第12代Core處理器將支援PCIe 5.0,並協同多家主機板廠商發表了第一批產品。這也讓PCIe 5.0進入主流處理器平臺的時間,比原先的預期提早一年以上,使得PCIe 5.0的應用環境初步成形。

PCIe 5.0從規格發布,到應用於x86平臺、構成初步應用環境,只花了短短2年,在PCIe規格發展史上,可說是異乎尋常迅速,比PCIe 4.0快一倍以上。

當前PCIe 5.0支援現況

雖然PCIe 5.0的應用仍處於起步階段,但已能涵蓋周邊裝置與主機領域,初步構成完整的應用環境。

在周邊裝置方面,ADATA、FADU、Kioxia與三星等廠商,都在2022年初的CES大會中,推出了支援PCIe 5.0的SSD新產品。在網路卡方面,Nvida的400Gb網路卡如ConnectX-7與BlueField-3,也都是採用PCIe 5.0介面。

在電腦與伺服器平臺方面,除了IBM Power 10平臺外,x86平臺方面目前只有Intel的第12代Core處理器(Alder Lake架構)支援PCIe 5.0,搭配Z690晶片組,各主要的主機板廠商也都已有相關產品上市。接下來,Intel預訂於2022年初推出的H670、B660與H610晶片組,也都會支援PCIe 5.0。在伺服器處理器方面,Intel預訂於2022年發表的下一世代Xeon處理器平臺Sapphire Rapids,也會有PCIe 5.0。

在AMD方面,則預訂於2022年推出的Zen 4處理器平臺上,引進PCIe 5.0。

PCIe 6.0的技術變革

在第一波PCIe 5.0產品陸續問世的同時,PCI-SIG也於2022年1月正式發表了下一代的PCIe 6.0規格。

PCIe 6.0可說是自從10多年前的PCIe 3.0以來,PCIe發展最重大的一次變革。如同過去幾個世代的升級,PCIe 6.0再次將傳輸速率翻倍,從PCIe 5.0的32GT/s提高到64GT/s,但採用了不同的信號編碼技術。

自PCIe 3.0延用到4.0與5.0的128b/130b NRZ編碼,隨著傳輸率的不斷提高,也給信號傳輸帶來越來越嚴苛的需求,導致線路長度上限越來越短,給元件設計帶來很大困難,要在同樣的技術路線下繼續提高傳輸速率,勢必會遭遇許多難以解決的問題,於是PCI-SIG在PCIe 6.0上改用PAM編碼。

PAM並不是新技術,普遍被應用於200Gb以上的超高速網路中,相較於只有0或1兩種信號狀態的NRZ編碼,PAM編碼有4個信號狀態,因而可在相同頻率內承載兩倍資料,但錯誤率也比NRZ高出許多,故 PCIe 6.0另外結合了前向糾錯技術(FEC)來確保資料完整性。至於這種新架構的代價,是PAM編碼的應用成本較NRZ高出許多,額外糾錯功能也會略為降低有效資料頻寬。

多頭並進的PCIe規格應用

彷彿是像追趕失去的時間一般,PCIe 規格正以異乎尋常的速度演進中。透過PCIe 5.0與6.0這兩種新規格,有助於將個人電腦與伺服器的I/O效能提升到新高度,但迅速演進的新規格,也造成不同世代規格同時並存的局面。

當前PCIe 4.0仍未充分普及,PCIe 5.0便已進入市場,接著又誕生了PCIe 6.0,這也讓PCIe的升級路線出現分歧。整體而言,PCIe 6.0規格才剛問世,預期最快兩年後才會有實際產品,可暫時不論,主要問題將出在PCIe 4.0與5.0之間。

固然目前PCIe 4.0的產品應用要比5.0成熟許多,但到了2022年下半與2023年初以後,PCIe 5.0的產品選擇將比現在豐富許多,成本也將下降,屆時對於既有的PCIe 3.0用戶來說,便有升級到PCIe 4.0,或直接跳到5.0的兩種選擇。

短期來看,可能會形成PCIe 4.0與5.0高低規混合應用的形勢,通用型主機與周邊裝置使用成本較低的PCIe 4.0,高效能型主機與周邊則用PCIe 5.0。但長期來看,若PCIe 5.0元件與周邊的成本下降得夠快,那麼直接跳到5.0世代或許更具吸引力。PCIe 5.0平臺可視情況使用5.0、4.0或3.0的周邊裝置,但PCIe 4.0平臺則無法發揮5.0裝置的效能,因而直接升級使用5.0平臺,將是更具靈活性的選擇。

熱門新聞

2026-02-02

2026-02-03

2026-02-04

2026-02-02

2026-02-04

2026-02-03

2026-02-05