去年上半,同為x86架構的兩大伺服器處理器平臺,陸續推出新一代產品,例如,3月15日登場的AMD第三代EPYC系列/7003系列(代號為Milan),4月6日發表的英特爾第三代Xeon Scalable系列(代號為Ice Lake)。

然而,從下半年起,又陸續掀起幾波關於後續產品的戰火,例如,英特爾在8月舉行的年度架構日、10月的Intel Innovation大會、11月的SC美國超級電腦大會,以至今年2月的英特爾投資大會,該公司均針對再下一代的伺服器處理器(代號為Sapphire Rapids),揭露了更多技術細節。

這幾年在伺服器處理器市占節節高升的AMD,則顯得保守許多,僅於去年11月SC大會前夕舉行的線上發表會AMD Accelerated Data Center Premiere,預告將推出配備3D V-Cache技術的EPYC 7003處理器(代號為Milan-X),

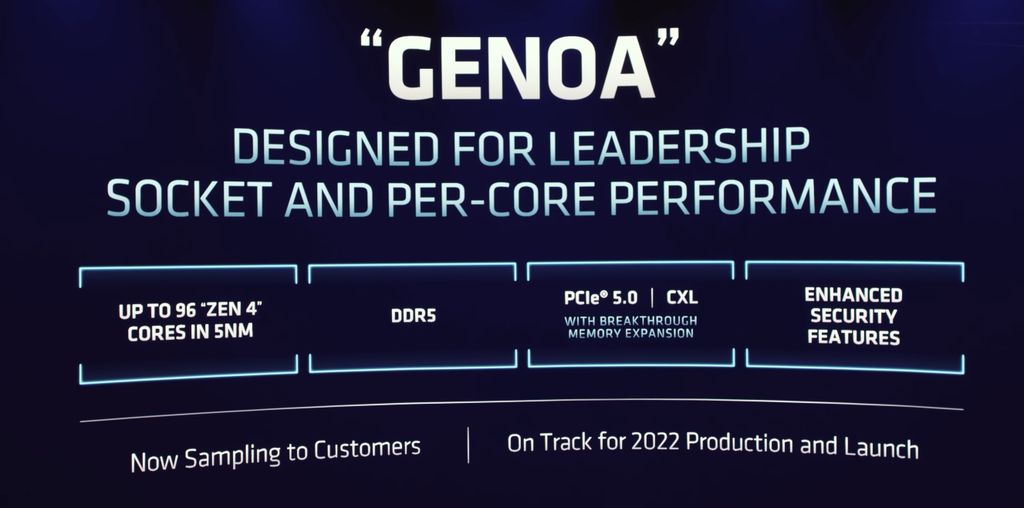

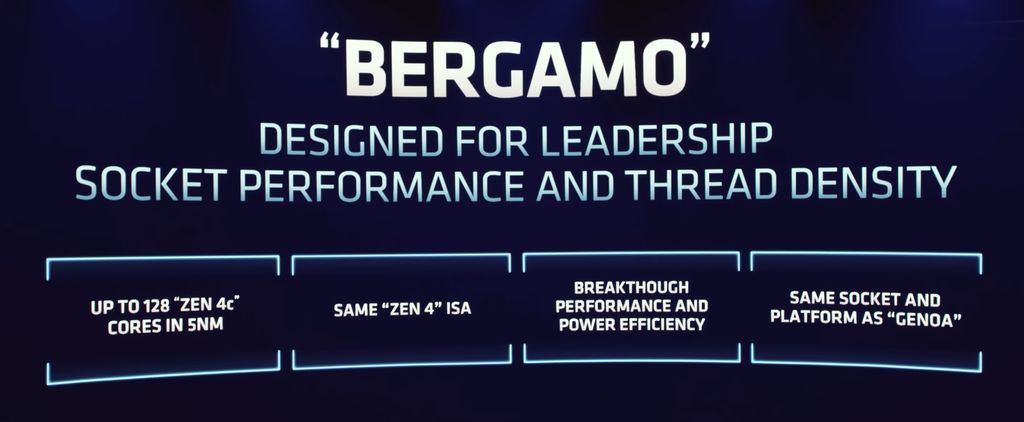

以及2022年發表下一代EPYC處理器(代號為Genoa),屆時將導入Zen4架構、5奈米製程,最多可提供96顆核心,並支援DDR5記憶體,以及PCIe 5.0與CXL等兩種I/O介面。

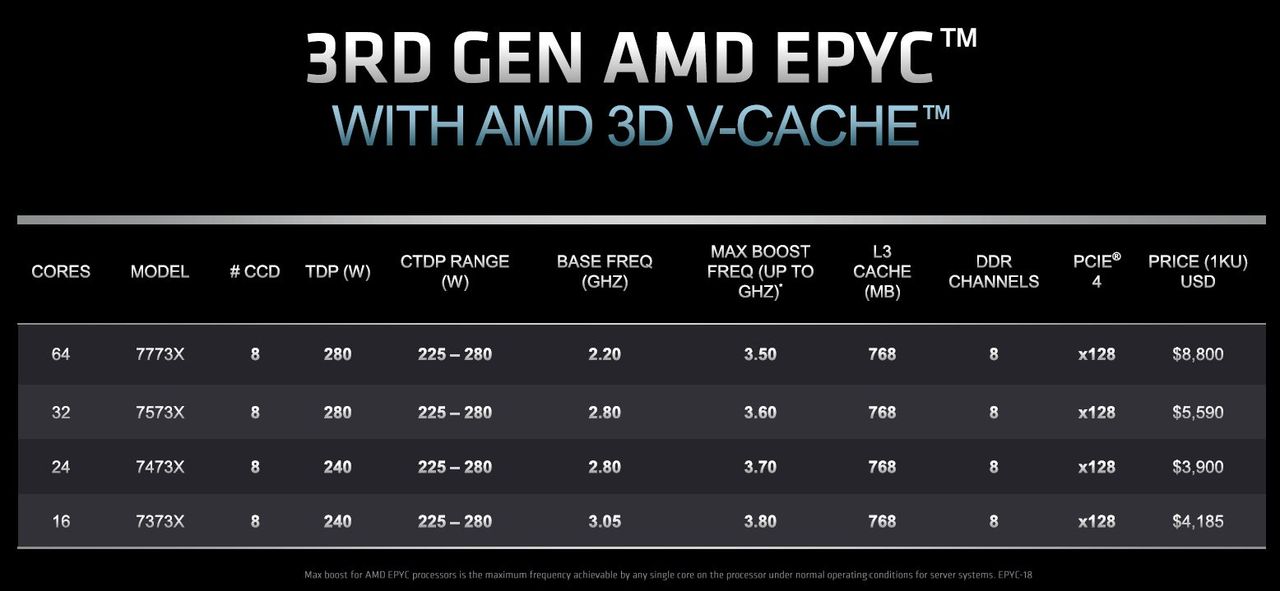

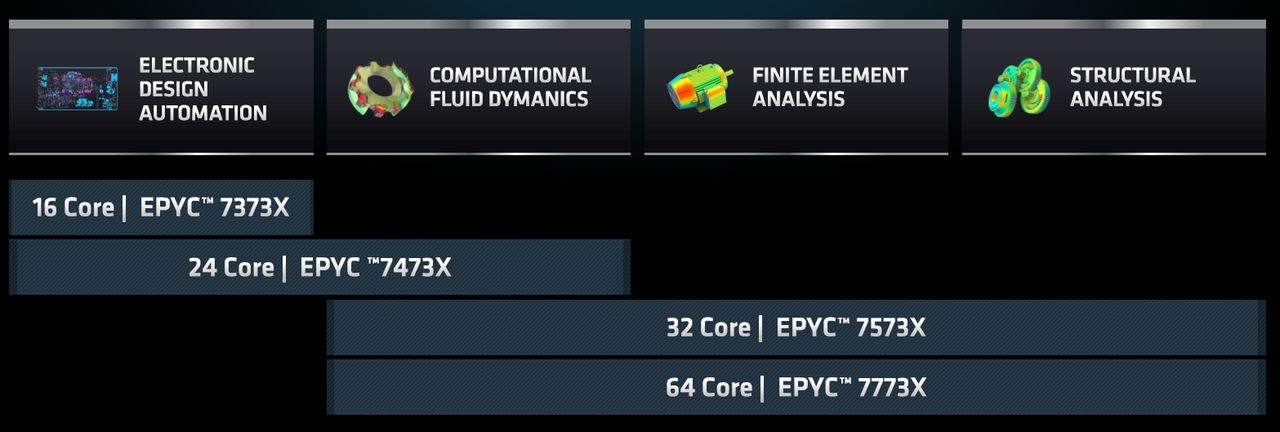

到了今年3月底,他們宣布,代號為Milan-X、採用3D V-Cache技術的第3代EPYC處理器正式推出,當中包含了4款機型:7373X、7473X、7573X、7773X,分別對應16、24、32、64顆運算核心的提供,而且全都配備多達768 MB的L3快取記憶體。相較之下,現行EPYC 7003系列處理器的L3快取記憶體組態有3種,分別是:64 MB、128 MB、256 MB。

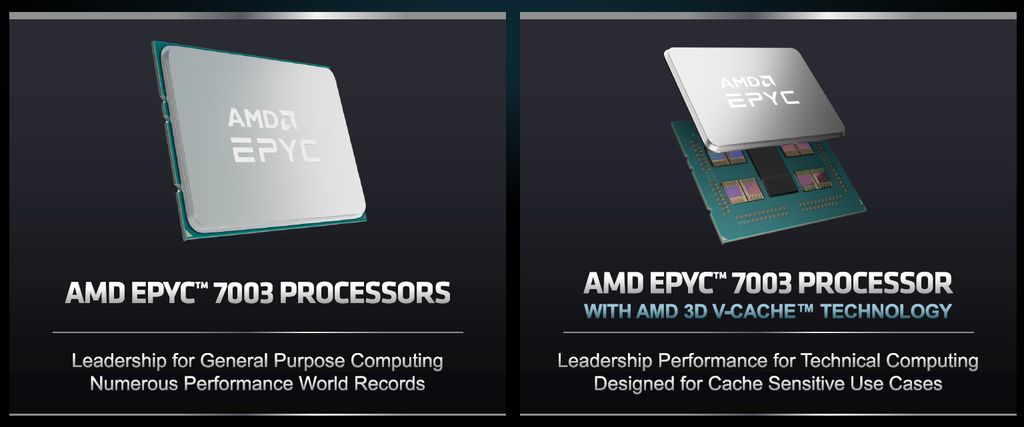

由於提供更大容量的L3快取記憶體,這4款新登場的EPYC 7003X系列處理器的定位,AMD認為,更適合執行工業運算類型(Technical Computing)的工作負載。

而這裡所謂的工業運算,主要是指下列應用類型,像是:電子設計自動化(Electronic Design Automation,EDA)、計算流體動力學(Computational Fluid Dynamics,CFD)、有限元素分析(Finite Element Analysis,FEA)、震波層析成像(Seismic Tomography)、氣象預測、量子力學、氣候研究、分子模擬。在這樣的應用場景之下,若以搭配既有EPYC 7003處理器的系統作為比較基準(16核心EPYC 75F3),最新發表的Milan-X可獲得66%的效能提升幅度(16核心EPYC 75F3X)。

採用3D裸晶堆疊技術,將L3快取容量垂直擴增至3倍

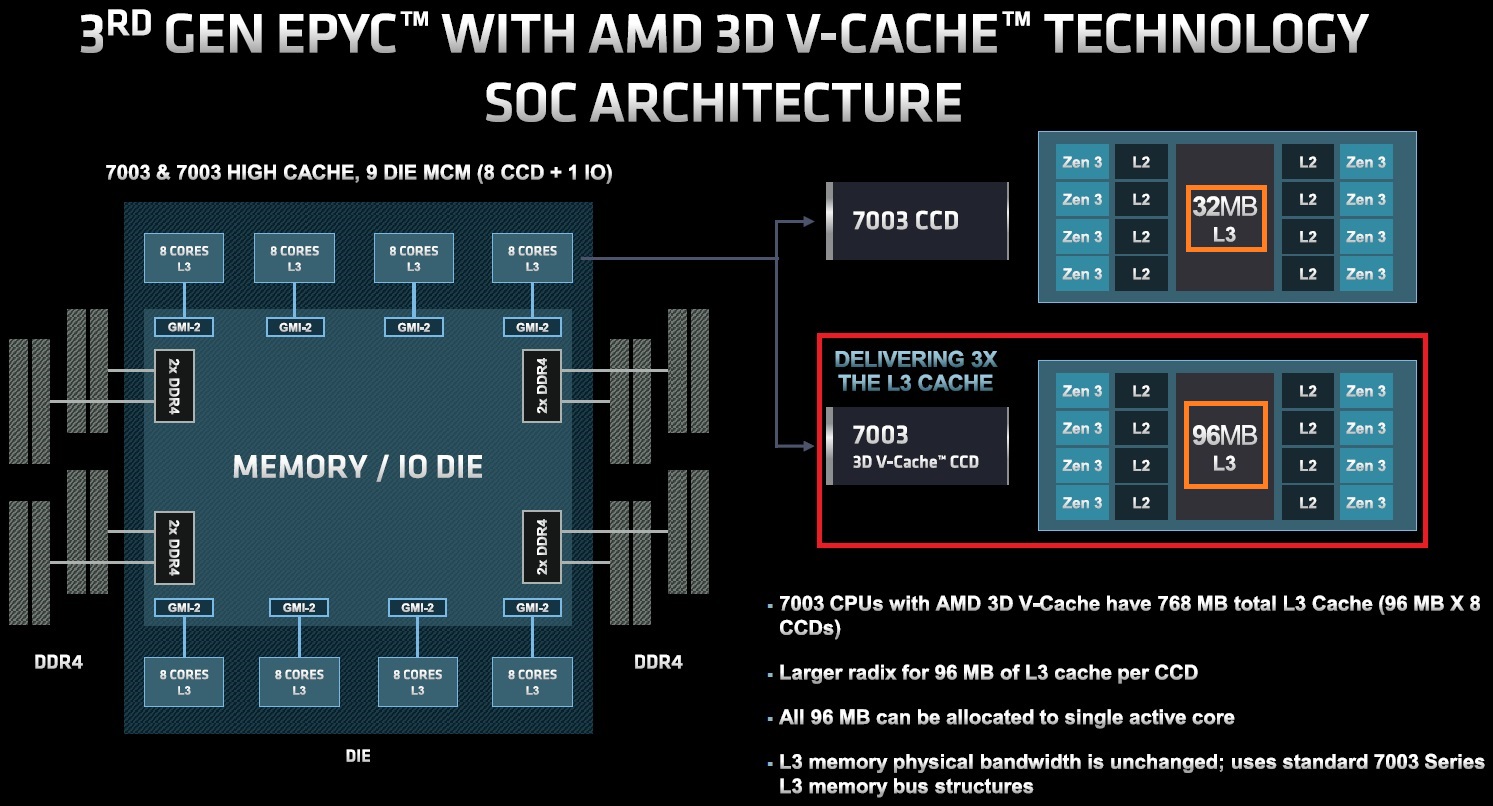

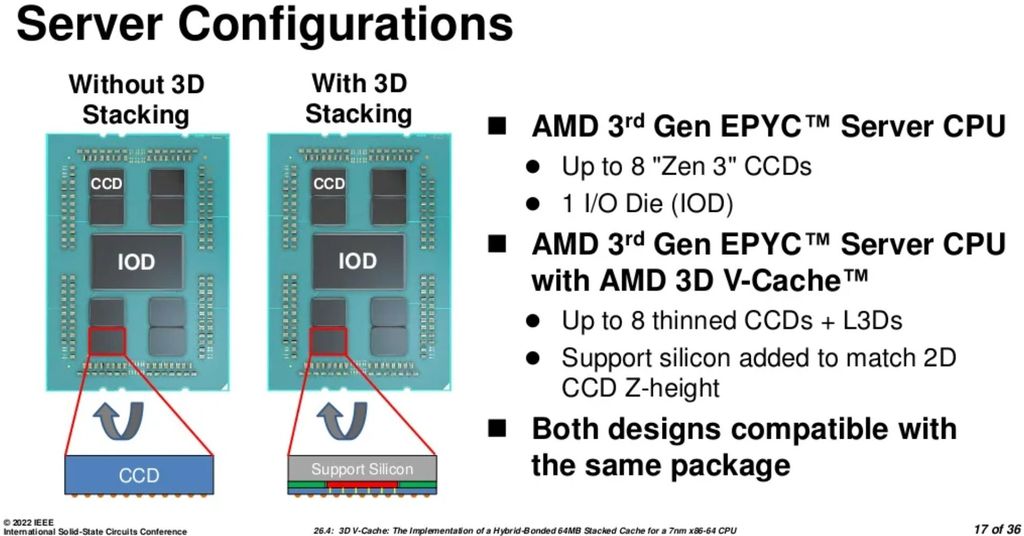

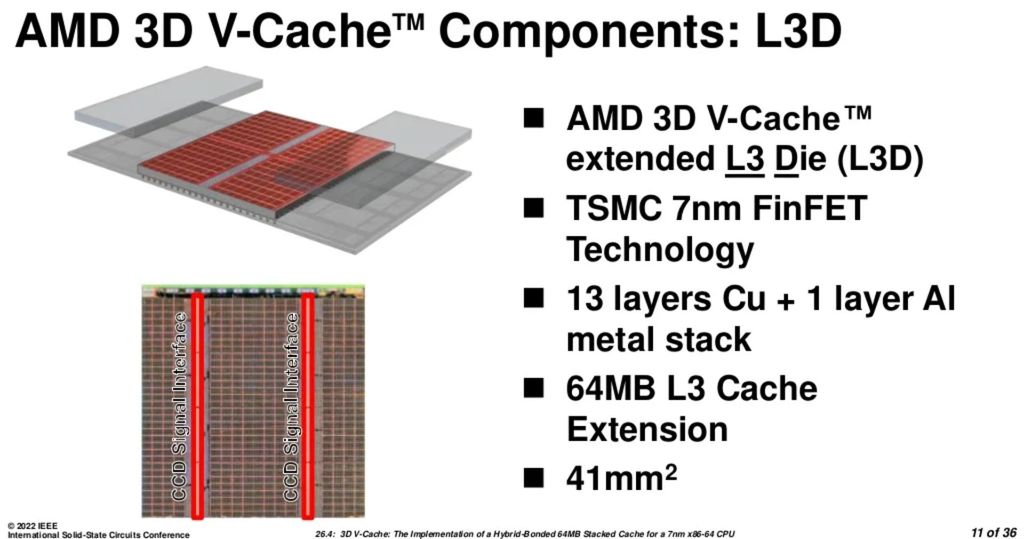

採用3D V-Cache技術的第3代EPYC處理器的推出,象徵AMD將垂直堆疊裸晶技術正式引進伺服器處理器。顧名思義,3D V-Cache是指透過3D垂直堆疊(3D Vertical stacking)的方式,擴充CPU當中的L3快取記憶體容量,以最新推出的EPYC 7003X這批主打大量快取的處理器機型為例,L3快取的容量可提升至既有7003系列處理器的3倍。

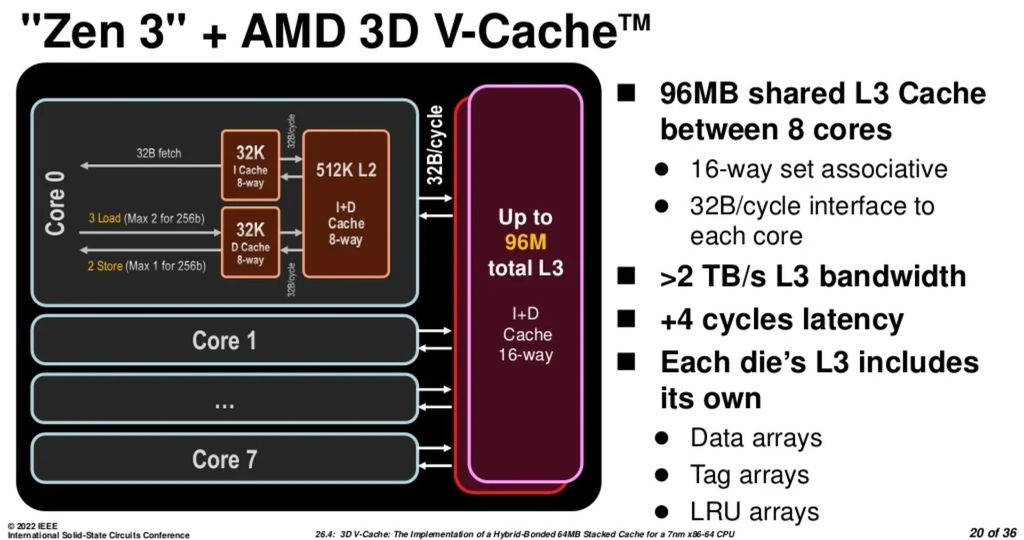

剖析EPYC 7003系列處理器的架構,目前多數型號的產品都包含8個核心複合體裸晶(Core Complex Die,CCD),若單就每個核心複合體(Core Complex,CCX)的組成而言,有8個Zen3核心運算單元、8個最大容量為4 MB的L2快取記憶體,以及共用的L3快取記憶體──先前發表的EPYC 7003系列處理器,此處的配置是32 MB,最新登場的EPYC 7003X系列處理器,因為導入了3D垂直堆疊的設計,而能將這裡的L3快取容量擴充至原來的3倍,成為96 MB,AMD表示,基於這樣的配置,意味著任何單一核心,不僅平均可使用的L3快取容量為12 MB,同時,也能完整存取到96 MB。

所以,若是從整顆處理器包含8個CCD的角度來看,此時L3快取記憶體的總容量就成為768 MB。

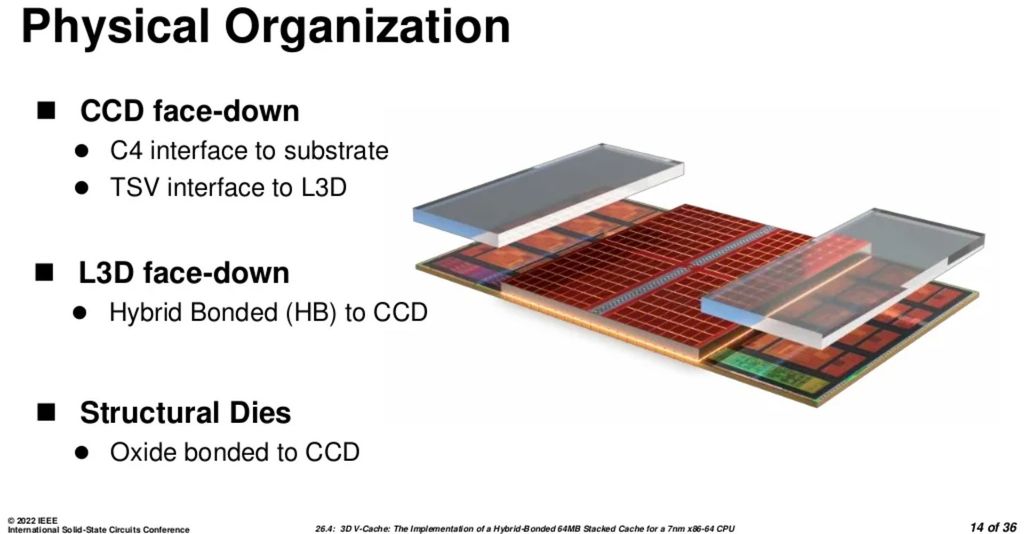

之所以能夠在此實現這樣的邏輯堆疊技術,AMD在今年1月發布了一篇關於進階封裝技術的部落格文章,針對他們與台積電合作、於去年臺北國際電腦展所提到的3D小晶片(Chiplet)技術,提出了更詳細的說明。

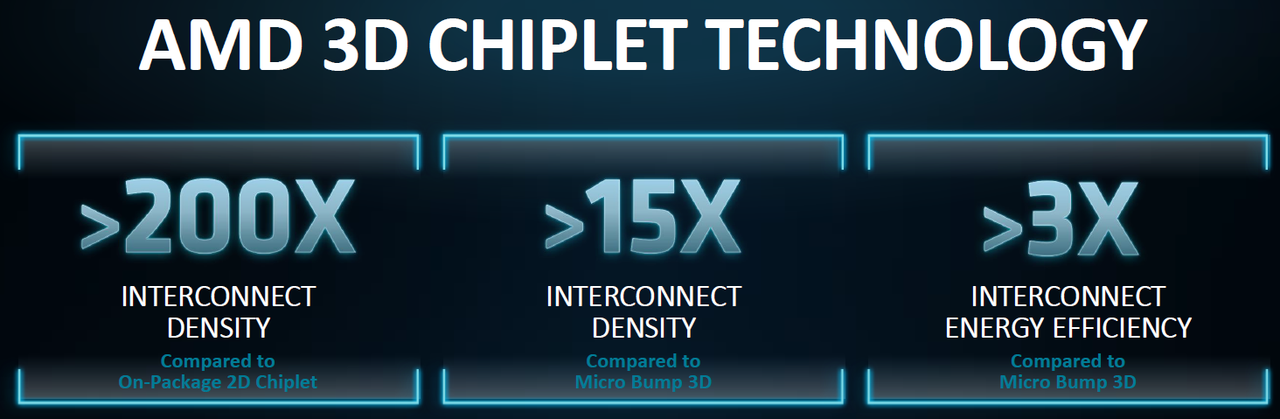

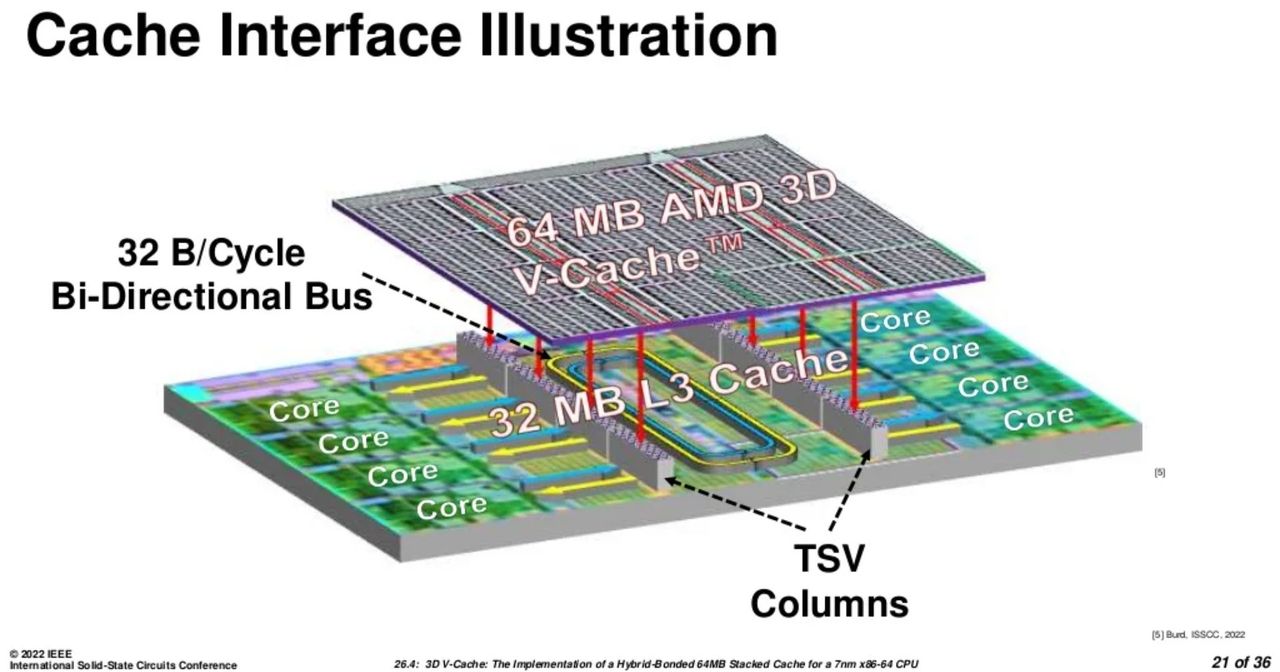

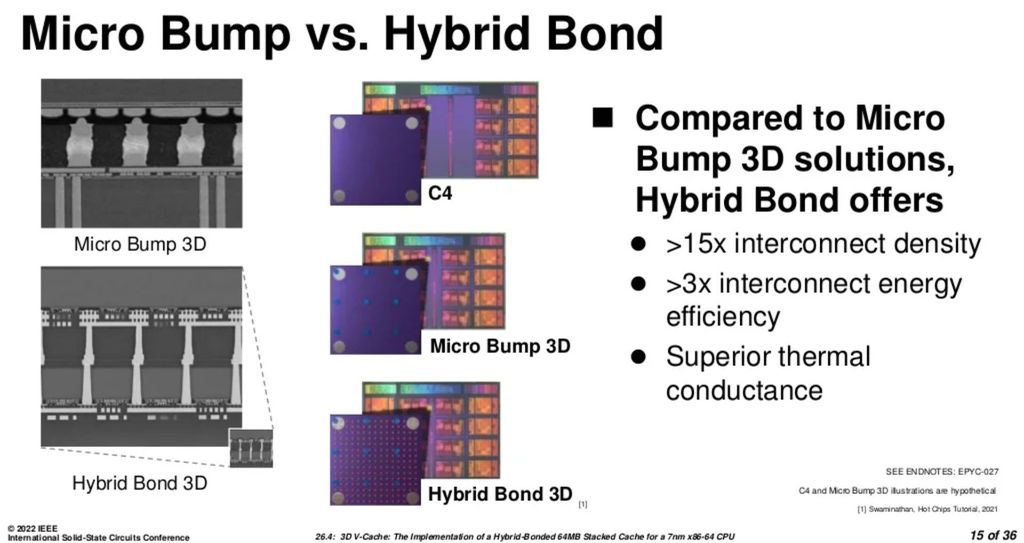

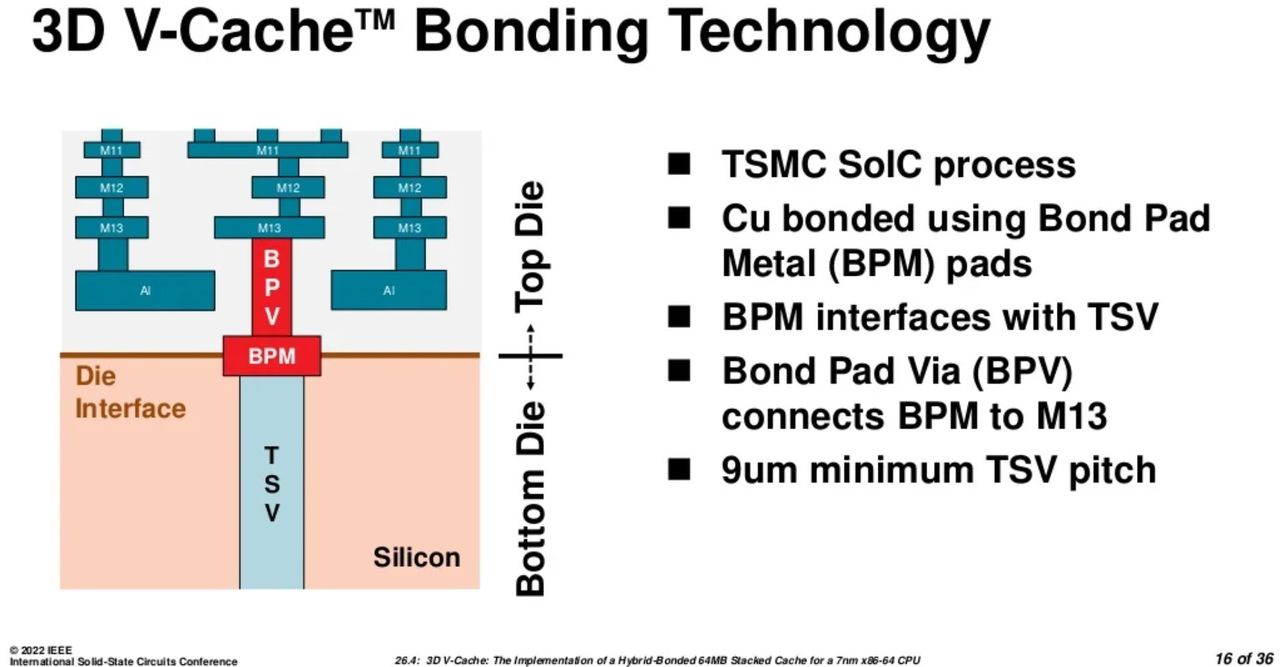

就成效來說,AMD表示,他們採用業界首創的混成黏接技術(hybrid bond),再加上矽穿孔(Through-Silicon-Vias,TSVs)的方法,而能將處理器的互連密度大幅提升──若以AMD自家發展的2D Chiplet技術為基準,可達到200倍以上;若以既有英特爾3D堆疊解決方案為基準(3D stacked micro-bump),可達到15倍以上。如此一來,就能以更有效率、更密集的方式,來整合AMD的硬體智慧財產。

如何實現這些作法?AMD主要是透過銅對銅(copper-to-copper)的直接黏結,構成了裸晶對裸晶(die-to-die)的介面,而不用任何類型的銲錫凸塊(solder bumps)來實現相關的設計,因此,可大幅改善電晶體密度與互連間距,超越其他的3D設計方式,進而成為具有更大使用彈性的矽晶片堆疊技術。

而在採用更小型的矽穿孔與銅對銅的直接連結之後,處理器對於每個訊號的處理電力大幅減少,若以採用其他微型3D凸塊設計方式而成的處理器為基準(英特爾Foveros),AMD提出的新作法,其單位耗電量不到三分之一,同時,SRAM至處理器CCD之間的總存取頻寬,也能因此提升至2 TB/s。

換言之,AMD認為,3D Chiplet技術能在最少的矽晶片面積上,提供最高的頻寬,而且,這樣的架構也能促成理想的散熱表現。

回溯技術源流,他們表示,AMD處理器採用的這些3D設計架構,有賴於台積電開發的混成黏接製程與3D Fabric技術。

適合特定領域的運算應用,能帶來相當顯著的效能提升

在產品定位上,由於EPYC 7003X系列處理器具有相當大的L3快取容量,針對特定應用領域,會有更突出的運算效能表現。

哪些工作負載適合這系列處理器?AMD列出3大類型,首先,是對於L3快取容量大小較敏感的應用型態;第二是對於大容量L3快取沒有命中與否考量的應用型態,像是:規模經常太大到超過大容量L3快取的資料集;第三是對於大容量L3快取沒有衝突與否考量的應用型態,例如,拖拉至快取的資料的彼此關聯性很低。

相反地,面對下列這3大類型應用,AMD認為,相對於EPYC 7003系列而言,EPYC 7003X系列較無明顯助益。首先,是L3快取命中率接近零的工作負載;第二,對於大容量L3快取沒有一致性考量的應用型態,像是在多顆核心之間高度共用的資料;第三是CPU密集型工作負載、卻只是串流資料,或只用一次、而非反覆地運作的應用。

關於運算效能的表現上,AMD也公布EPYC 7003X系列處理器在工業運算多種領域當中的改善幅度。

以電子設計自動化為例,同為16核心的7373X對上73F3,執行Synopsys的半導體模擬與驗證軟體VCS時,在模擬速度上,領先幅度為66%;

在計算流體動力學應用中,同為32核心的AMD EPYC 7573X對上英特爾40核心Xeon Platinum 8362,均以2路架構來執行Ansys的渦輪機應用軟體CFX時,每天平均解決的問題數量比例高出88%;

若是有限元素分析的應用,2顆AMD 64核心的EPYC 7773X對上2顆英特爾40核心Xeon Platinum 8380,執行Altair的產品效能評估軟體 Radioss模擬應用程式時,平均效能領先44%。

熱門新聞

2026-02-06

2026-02-09

2026-02-06

2026-02-09

2026-02-06

2026-02-06