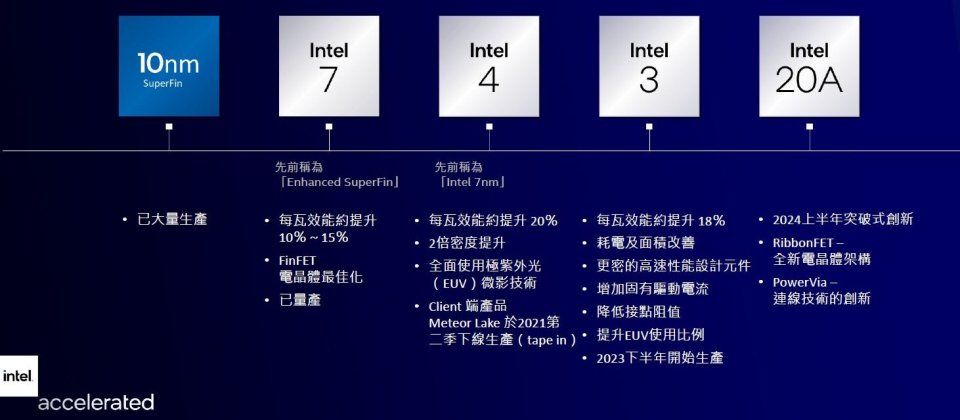

英特爾本周二公布最新節點命名方式,並預告未來4年將從Intel 7、4、3,發展至Intel 20A,以及正在研發中,將於2025年採用的Intel 18A。

Intel

英特爾執行長Pat Gelsinger上任後,今年3月對外宣布將啟動IDM 2.0(Integrated Device Manufacturing 2.0)的重大策略,準備大舉重振英特爾的晶圓代工事業(Intel Foundry Services,IFS),同時加速該公司在半導體技術的革新,試圖扭轉外界對其製程技術發展緩慢的劣勢。

本周英特爾在加速日的線上活動中,公布最新製程技術發展藍圖,從今年開始採用新的節點命名方式,包括Intel 7(即先前的10nm Enhanced SuperFin)、Intel 4(先前的Intel 7nm)、Intel 3,為節點命名建立一致性的框架,該公司強調此舉讓其客戶、產業對其製程節點有更精確的認知。

另外,2024年將從「奈米」(nanometer)進入「埃米」(angstrom)時代的Intel 20A,開始採用RibbonFET的英特爾環繞式閘極(Gate all around)電晶體,以及PowerVia的背部供電設計,強調能最佳化訊號傳輸。而在Intel 20A之後,將在2025年初問世的Intel 18A正在研發中,將採用改良的RibbonFET及下一代EUV微影技術。此外,英特爾宣布IFS已獲得AWS、Qualcomm支持,將採用其製程及封裝技術。

英特爾採用新的節點命名架構,頗有扭轉長久以來外界對其製程落後晶圓代工業者的批評之意,例如英特爾仍採用10奈米,而晶圓代工業者台積電早已進入7奈米製程,去年第二季宣布成功量產5奈米FinFET製程技術,並預告2022年準備量產4奈米製程技術,未來還將發展至3奈米。

根據英特爾說明,Intel 7雖仍為10奈米製程技術,但採用enhaced FinFET,每瓦效能比Intel 10nm SuperFin提高10到15%,至於Intel 4才是採用7奈米製程,每瓦效能較Intel 7提升20%。值得注意的是,此處每瓦效能提升係指製程技術的改進,並非最終處理器產品的效能。

對於英特爾新的節點命名要如何對應到台積電的製程技術?英特爾創新科技總經理謝承儒解釋,英特爾考慮新的節點命名方式,參考業界普遍使用的重要參數,例如以每瓦效能的表現決定是否進入新的節點,因此英特爾參考業界命名的參數標準,將原本的Intel 10nm enhanced SuperFIN改為Intel 7,以接近產業界的7奈米,以較簡單的方式簡化節點命名。

換言之,Intel 4、Intel 3、Intel 20A未來將對應到數字接近的其他業者製程。

英特爾大動作宣布加速製程封裝技術,從2021年Intel 7到2024年的Intel 20A,甚至2025年之後的Intel 18A,未來4至5年內,英特爾製程技術將翻新5次,可能牽動英特爾旗下處理器產品發展。

回顧過去英特爾製程技術與產品發展,例如在45奈米製程時,採用Hi-K金屬閘極技術,以改善電晶體漏電流的問題,而在跨入32奈米製,進一步採用第二代Hi-K金屬閘極技術,應用在資料中心的Westmere產品。2014年英特爾公布首批處理器開始採用14奈米製程生產,採用第二代三閘極(Tri-gate)FinFET電晶體。

而在本周英特爾公布製程技術的同時,也明確指出Intel 7將在2021年用於用戶端產品的Alder Lake,2022年用於量產資料中心產品Sapphire Rapids,而採用EUV極紫外光微影技術,每瓦效能比Intel 7提升20%的Intel 4,也會在2022到2023年間用於用戶端的Meteor Lake及資料中心端的Granite Rapids。

英特爾啟動IDM 2.0,數年內密集更新技術,希望藉此提升製程封裝技術,但同時間內多項專案並行,勢必考驗英特爾的技術研發能力。

熱門新聞

2026-02-11

2026-02-11

2026-02-09

2026-02-10

2026-02-10

2026-02-06

2026-02-10