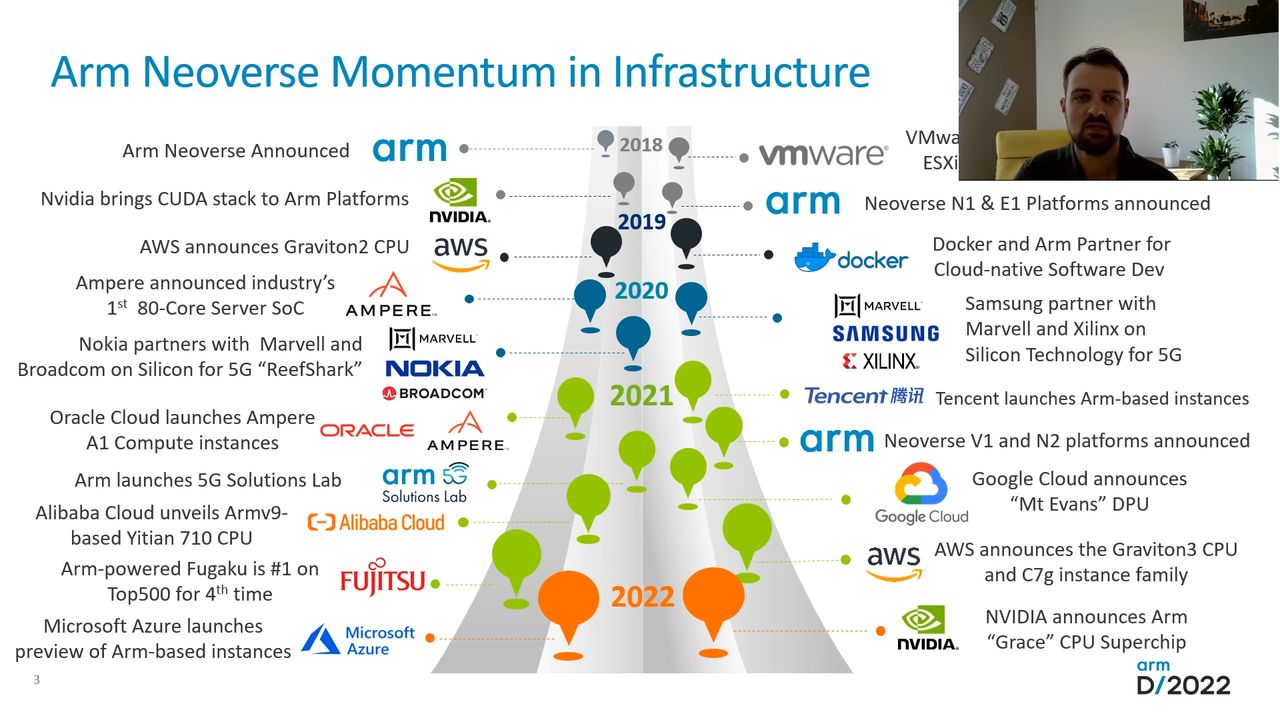

這三年來,Arm架構挺進高效能運算、雲端服務資料中心領域,獲得重大突破之餘,也頻頻取得相當亮眼的成績。

以伺服器級處理器為例,採用富士通設計A64FX處理器的超級電腦Fugaku,蟬聯2020年與2021年的全球500大超級電腦冠軍,今年退居第二;Arm於2018年10月成立邊緣至雲端服務產品線Neoverse ,公有雲服務龍頭廠商隨即於11月底的全球用戶大會,發表自製Arm架構處理器Graviton,以及Arm架構執行個體服務Amazon EC2 A1,之後陸續推出採用Arm Neoverse N1平臺的Graviton2,以及Arm Neoverse V1平臺的Graviton3處理器,以及多款Arm架構執行個體服務。

而在伺服器應用的發展上,Ampere Computing公司2020年推出Altra系列與Altra Max系列處理器,這兩款產品都是採用Arm Neoverse N1平臺,伺服器廠商則以技嘉科技為首,陸續推出多款搭配Ampere公司處理器的運算設備,打造出Mt.Snow平臺,近期出現更多廠牌發表這類產品,像是緯穎科技在2020年3月發表SV328,2021年向開放運算計畫(OCP)提交Mt. Jade主機板規格。

HPE在6月發表ProLiant RL300 Gen11,10月底公開產品細部規格;浪潮同樣在年中發表NF5280R6,並在10月底向OCP提交Mt. Mitchell主機板設計。除了這些廠商,Supermicro、鴻海工業富聯也與Ampere公司合作,各自發展Mt. Hamilton、Mt. Collins等主機板規格,而在產品的部分,鴻海工業富聯已於今年5月宣布推出兩款機型:R-2110、R-2211,Supermicro悄悄在網站公布一款機型的規格與資訊,名為MegaDC SuperServer ARS-110M-NR。

由於市面上出現更多Arm伺服器的選擇,從2020年底起,其他公有雲業者與資料中心代管服務商也紛紛釋出消息,表示正在評估或有意推出基於Ampere公司處理器的執行個體服務,像是Oracle Cloud Infrastructure、微軟Azure、Cloudflare、Equinix、阿里雲、騰訊雲、Google Cloud。

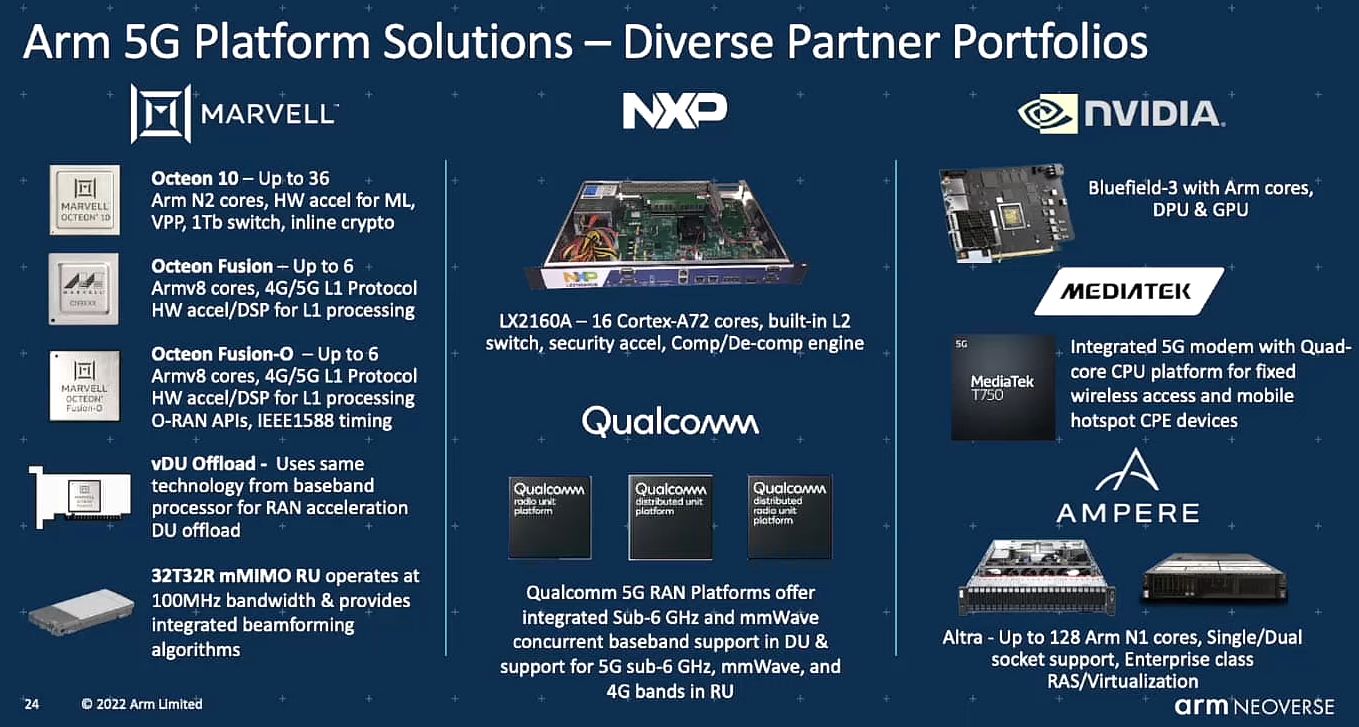

值得注意的是,Arm架構在資料中心領域還有另一條發展路線,那就是資料處理器(DPU)類型的加速運算。

回顧過去,多家網路介面晶片與FPGA晶片廠商,陸續推出搭配Arm處理器的擴充介面卡,像是可卸除特定工作負載的加速卡、SmartNIC智慧型網路卡,隨著5G vRAN應用、電信服務業數位轉型,以及雲端服務、高效能運算等環境的盛行,順勢打開了新的IT基礎架構市場,也衍生出現今備受矚目的多種DPU產品,像是:Nvidia的BlueField系列,Marvell的Octeon系列,AMD的Xilinx Alveo系列與Pensando系列、英特爾的IPU系列,另外,雲端服務業者AWS也設計出Nitro Cards,供自家基礎架構平臺搭配使用。這些產品或解決方案當中,也都搭配了Arm架構CPU或運算核心。

公布Neoverse最新發展藍圖,發表V2平臺與E2平臺

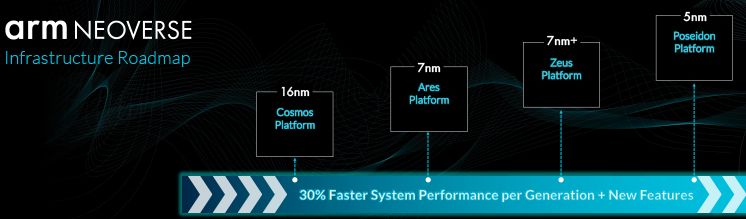

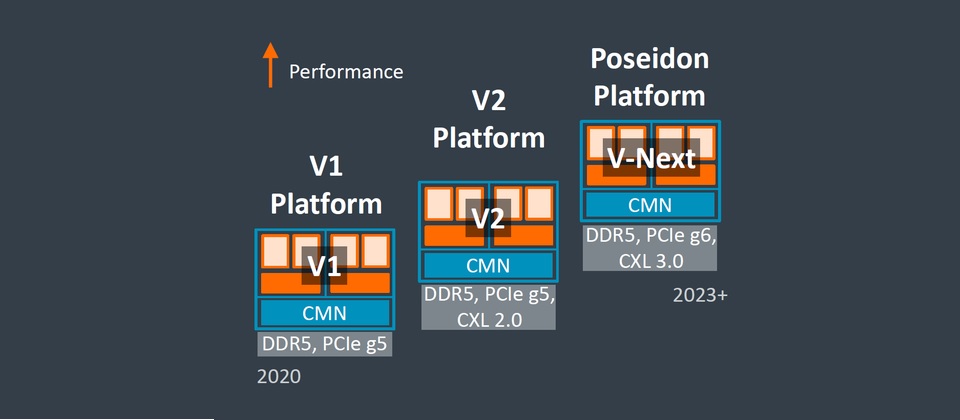

隨著Arm設立Neoverse系列產品線,以及逐漸區分出不同平臺之後,後續各家廠商發展的Arm架構伺服器處理器與資料處理器,也有了共同依歸。例如,2018年10月Arm首度公開Neoverse發展藍圖,以處理器製程區,分為4個世代的平臺,代號依序是:Cosmos為16奈米製程,Ares為7奈米製程,Zeus為7+奈米製程、Poseidon為5奈米製程;2019年2月,Arm發表了Neoverse N1與Neoverse E1。

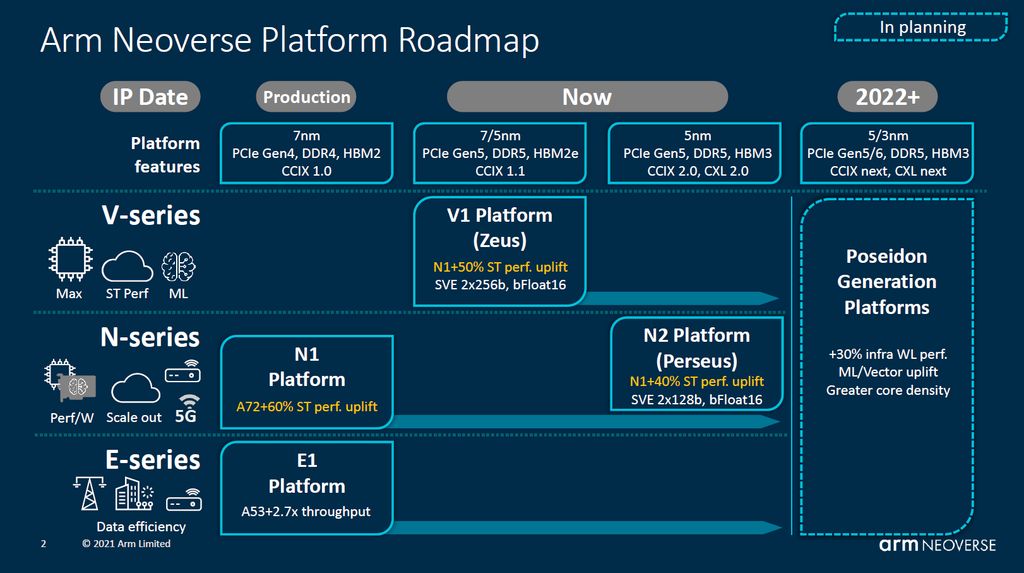

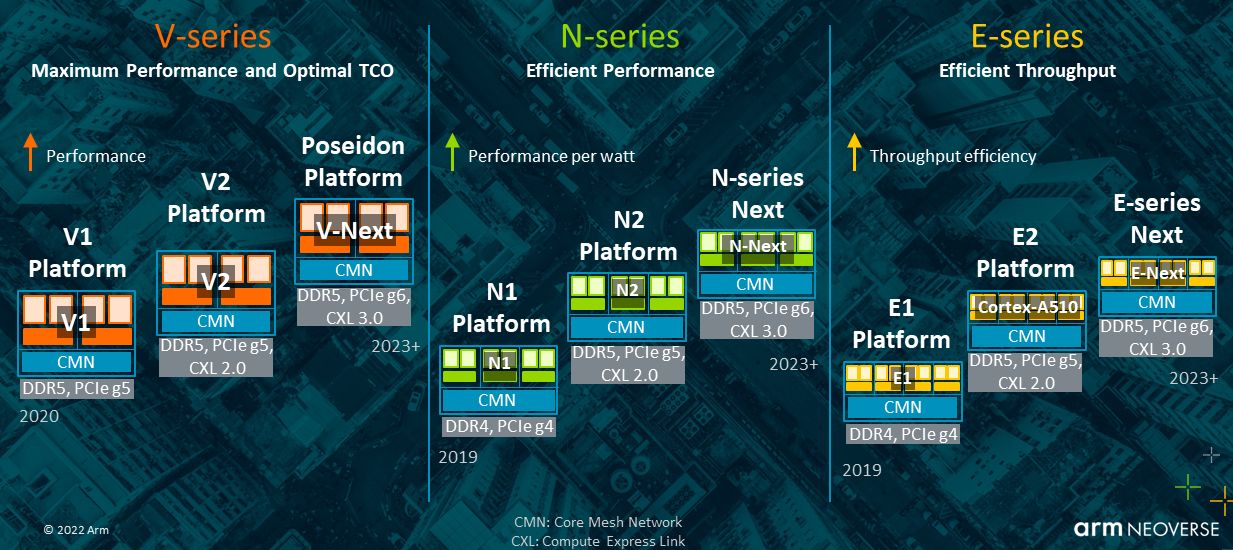

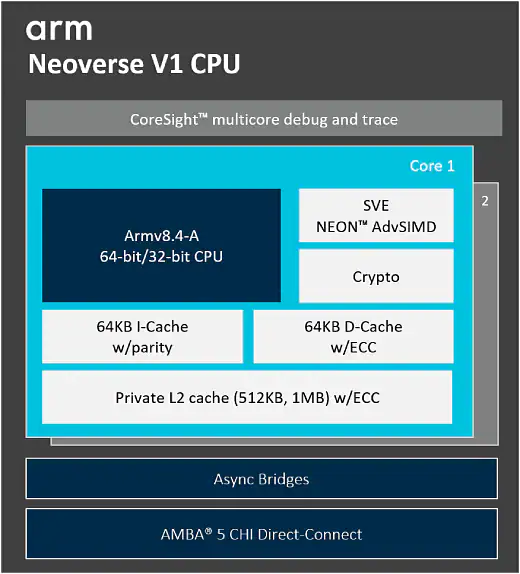

2020年9月,Arm更新Neoverse發展藍圖,平臺擴展為三,分別是追求極致效能的V系列,訴求每瓦效能、適合橫向擴展規模的N系列,主攻低功耗、高吞吐量的E系列,並宣布推出V1與N2等兩個平臺。對照先前的規畫,Neoverse第一波產品的確導入了7奈米製程,而N1是先前提到的Ares平臺,E1則是後續新增的,它們可支援PCIe 4.0介面、DDR4記憶體、HBM2高頻寬記憶體、CXL 1.0記憶體擴充介面,以及快取一致性互連介面CCIX 1.0;本次發表的V1是Zeus平臺,開始支援SVE2指令集、BFLOAT16資料格式,屬於Neoverse第二波產品,導入7奈米與5奈米製程,可支援PCIe 5.0介面、DDR5記憶體、HBM2e高頻寬記憶體、CXL 1.1記憶體擴充介面、CCIX 1.1。

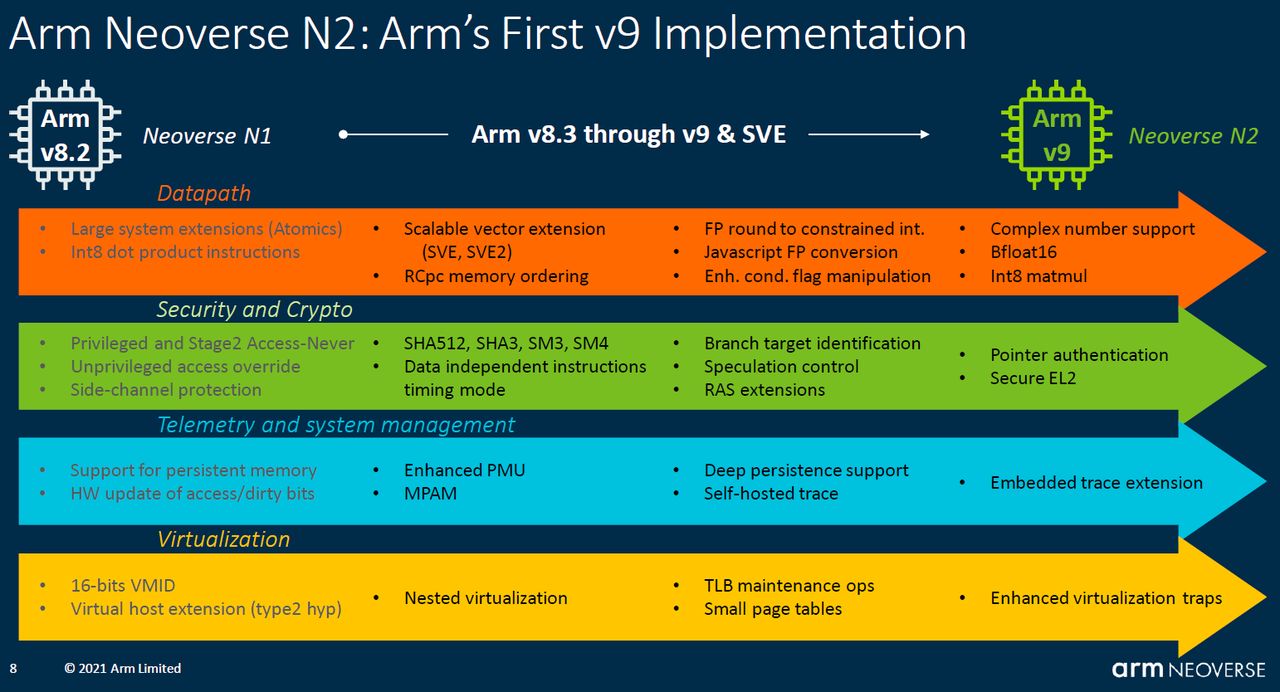

而在原本的Zeus與Poseidon之間,Arm預告在2021年將推出代號為Perseus的N2平臺,這是第一款導入Armv9架構的Neoverse平臺,因此內建SVE2指令集,而在運算方式上,也支援BFLOAT16資料格式,而在整體規格上,N2導入5奈米製程,可支援PCIe 5.0介面、DDR5記憶體、HBM3高頻寬記憶體、CXL 2.0、CCIX 2.0。至於最終的Poseidon,預計導入5奈米與3奈米製程,可支援PCIe 5.0與6.0介面、DDR5記憶體、HBM3高頻寬記憶體,以及下一代的CXL與CCIX。

在這兩年來,我們陸續看到許多廠商推出基於Neoverse平臺的Arm架構處理器。其中最受歡迎的是Neoverse N1,以伺服器處理器而言,有AWS的Graviton2,以及Ampere的Altra系列與Altra Max系列;而在資料處理器的部分,則有英特爾的IPU E2000(代號Mount Evans)。採用Neoverse N2的例子,也逐漸增多,像是阿里雲的倚天710(Yitian 710)、Marvell 的Octeon 10 DPU。

對於Neoverse V1的運用,AWS去年底發表、今年5月正式上線的EC2 C7g執行個體服務,底層伺服器硬體搭配的Graviton3處理器,就是基於這個Arm平臺而成。

到了9月中,Arm再度揭露Neoverse最新發展藍圖,當中增列V2平臺(代號為Demeter)及E2平臺,並且調整三大系列與各個平臺推出時程的呈現方式。

回顧2020年公布的Neoverse發展藍圖,Arm先由上至下列出V系列、N系列、E系列,再依照推出時間先後橫列各個平臺,例如,V系列只有V1,N系列有N1與N2,E系列只有E1,在2022年之後均統稱為Poseidon世代的平臺。

而今年最新發布的Neoverse發展藍圖,可能是因為平臺增多與有意突顯各個平臺差異的關係,改為由左至右列出V系列、N系列、E系列等三個排面,而在每個系列當中,再依照推出時間先後與效能高低排列各個平臺的位置,如此一來,可同時突顯每個系列不同平臺的上市時程,以及效能節節高升的狀態,讓大家了解各系列名稱之後搭配的數字大小,不僅意味著發表的先後順序,也有著效能與效率的差異。

除此之外,Arm也首度在這類產品資訊當中,標示另一個Neoverse搭配的系統單晶片關鍵元件「一致性互連網路(Coherent Mesh Network,CMN)」。這裡同時揭示了Neoverse下一世代V系列、N系列、E系列的發展,預告將支援PCIe 6.0與CXL 3.0。

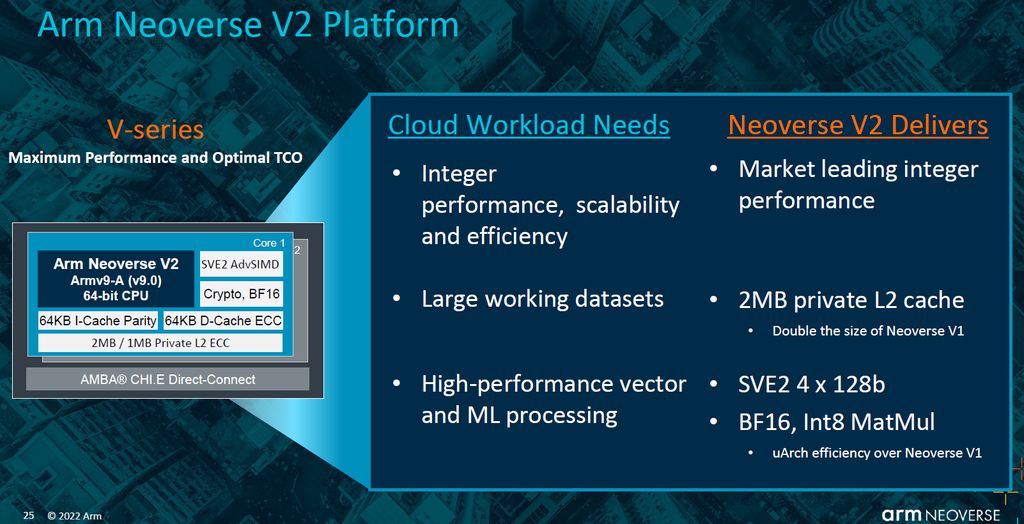

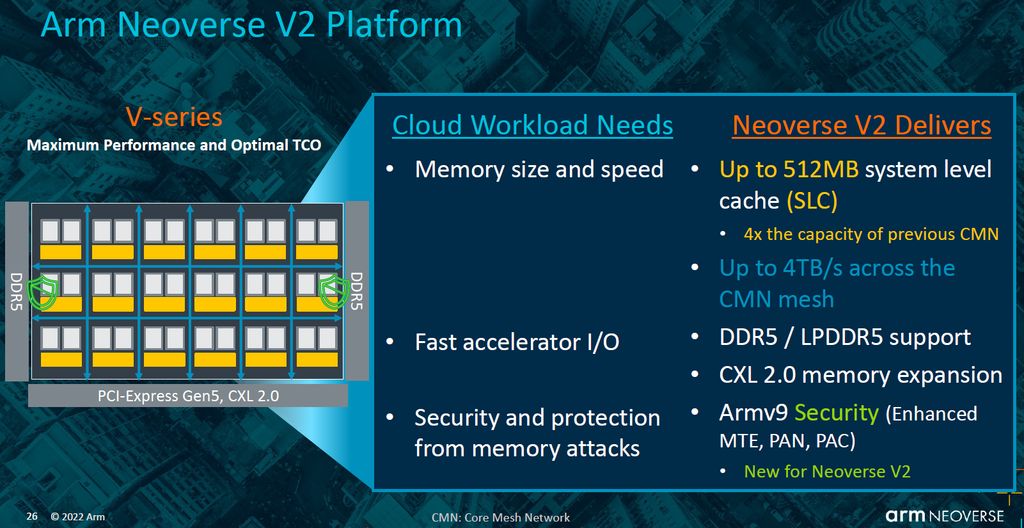

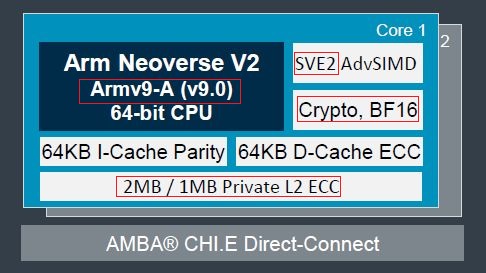

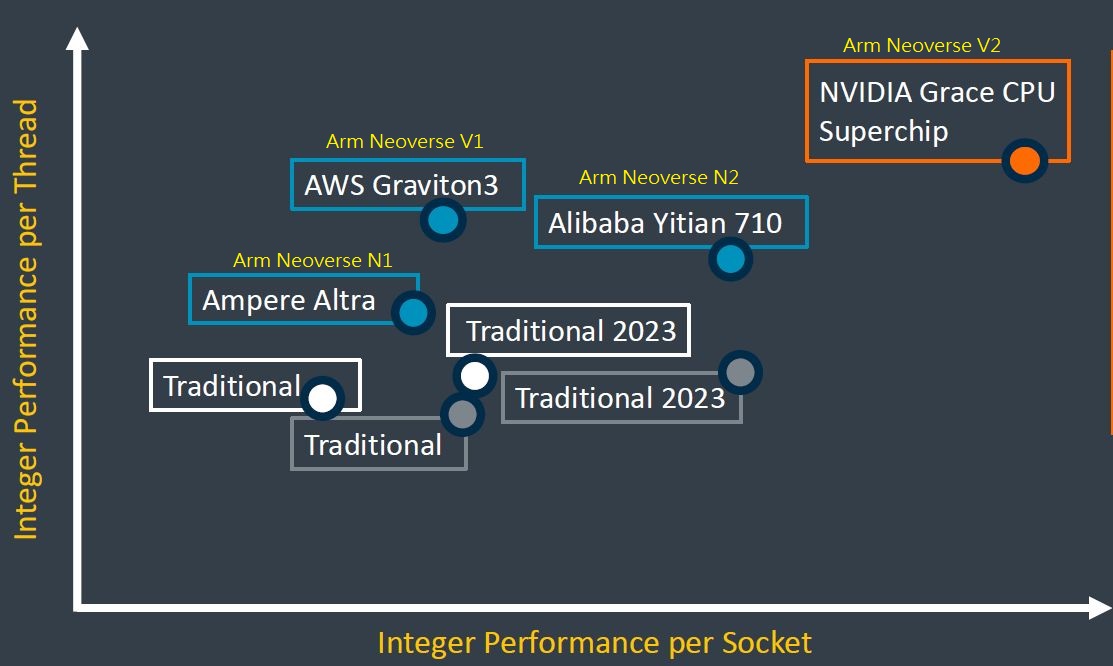

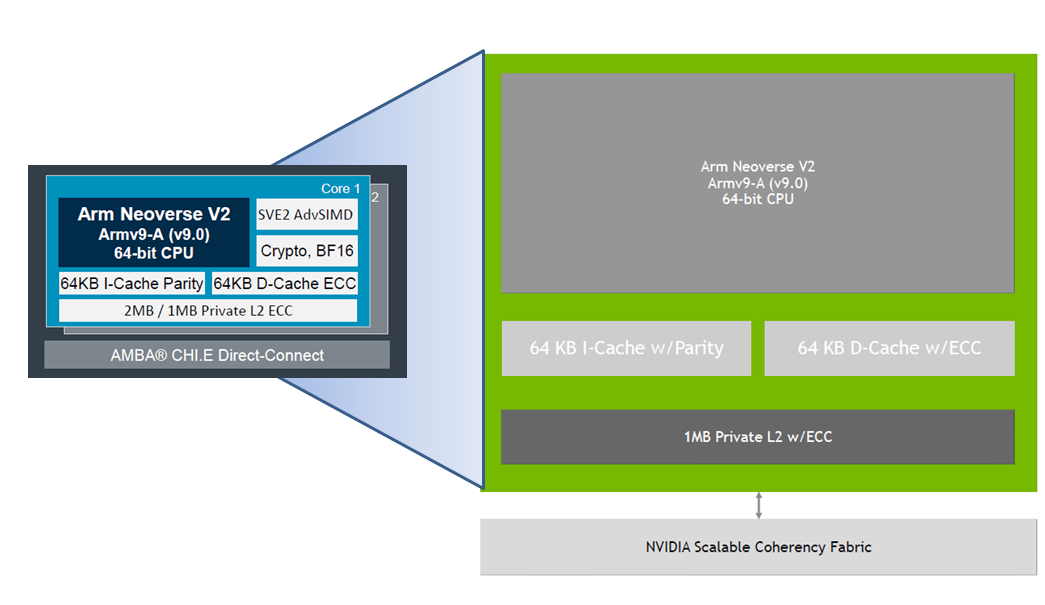

而最新發表的Neoverse V2當中,Arm著重在雲端服務工作負載的表現上,首先是提供更強大的整數運算效能,以因應雲端環境最基本的需求,便於維運人員擴展執行規模,獲得良好的能源使用效率,能讓業者提供更多運算核心,使每一臺伺服器服務更多用戶,從而降低成本,再將成本節省效益回饋用戶;第二,則是針對大型資料集的處理,一般而言,就近在處理器層級盡可能保留更多資料,將會帶來更大的存取效能,Arm為此在Neoverse V2核心架構當中,提供2MB容量的自用L2快取記憶體配置,比起Neoverse V1增加了1倍,而在延遲度與V1相同的狀態下,Neoverse V2對於MySQL、Memcached資料庫務應用,提供更可觀的效能突破。

第三個特色,則與在雲端環境執行高效能運算、機器學習等類型工作負載的趨勢有關,使得向量處理效能的重要性與日俱增,Arm在新推出的Neoverse V2提出對策,是將內建可擴展向量延伸指令集(SVE)升級到第二代(SVE2),可處理更多類型工作負載,也增添更多密碼學處理指令。對於SVE引擎的設計,Arm也進行重構,將其改為4個128位元通道,並且調校微架構,強化系統層級的有效吞吐量。

Neoverse V2針對的第四個面向,是DRAM記憶體資源的使用,雲端業者盼望能支援更大的容量與更快的存取速度,使其能夠推出每顆CPU核心搭配高存取頻寬記憶體的執行個體服務,而這也成為驅動大型雲端工作負載的重要因素,另一方面,雲端業者的伺服器需要跨越整個I/O匯流排,連接GPU、TPU這類運算加速器,以及NVMe固態硬碟,促使整個平臺必須提供更快的存取速度,支援更高的頻寬。

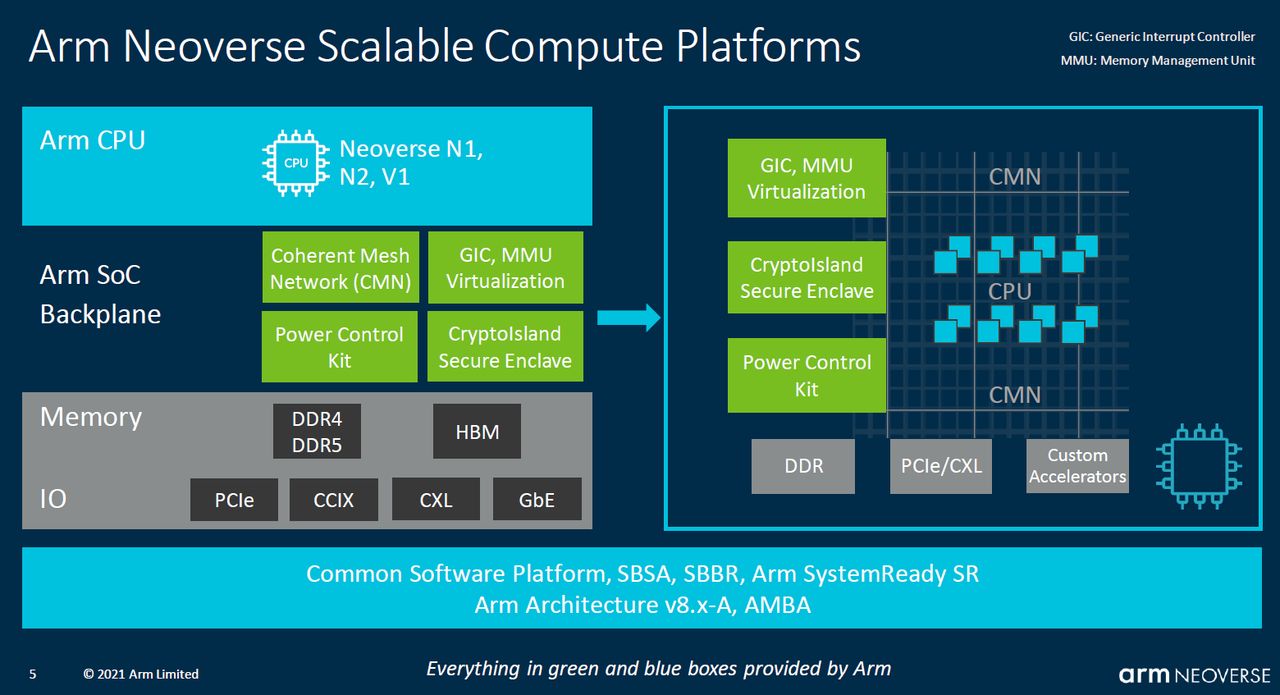

而在Arm與合作廠商開發Neoverse V2的過程中,他們運用系統層級的背板智財為Neoverse平臺提供支援,包含CMN互連網路、錯誤管理單元(FMU)、Gig,以及其他非一致性的互連方式。

舉例來說,Neoverse V2可搭配系統互連元件CMN-700,此時對於每顆晶粒的搭配使用,最大可支援512 MB容量的系統層級快取記憶體(SLC),而這樣的設計,有助於提升雲端原生工作負載的效能。關於CMN-700的使用,Arm表示目前支援2.5D封裝的設計,不過,他們發展的平臺已完成轉移到3D封裝的準備,屆時可將每顆核心能夠搭配更大容量的快取記憶體。

除此之外,CMN-700對於整個互連架構可支援的最大頻寬為4 TB/s,基本上,CPU若需使用HBM2e高頻寬記憶體的設計,需要0.5 TB/s的頻寬,對此,Arm自認CMN-700提供足夠的互連頻寬餘裕,可透過這樣的搭配來因應處理規模較大的應用程式。

在資安防護方面,Neoverse V2因為導入Armv9架構而獲得多種安全性新特色,可因應記憶體層級的攻擊,像是進階的記憶體標記延伸技術(Memory Tagging Extension,MTE)、特權存取禁用(Privileged Access Never,PAN)、指標驗證碼(Pointer Authentication Code,PAC)。

採用Neoverse V2平臺的產品浮出檯面:Nvidia第一款伺服器CPU

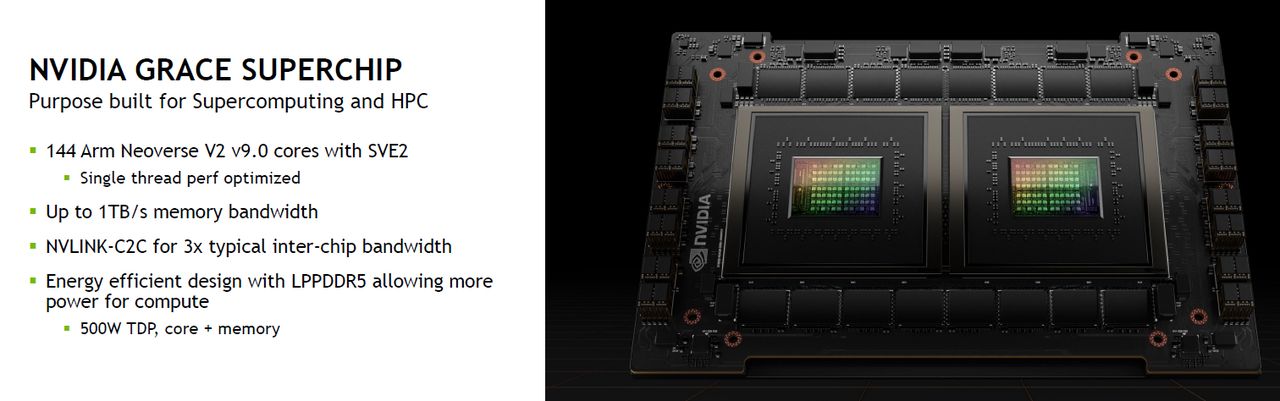

而在9月發表Neoverse V2之際,Arm表示已有多家廠商基於這個平臺正在設計產品,其中之一,正是Nvidia去年4月預告、2023年即將推出的伺服器處理器Grace,在今年8月底舉行的Hot Chips大會與9月舉行的GTC 2022秋季大會,Nvidia終於揭露更多Grace系列處理器的相關資訊。

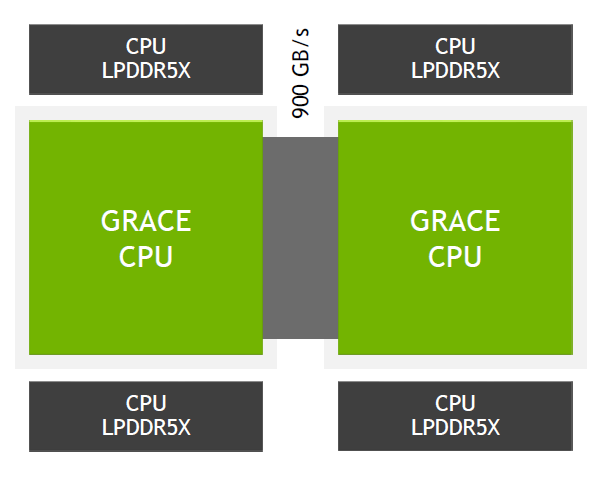

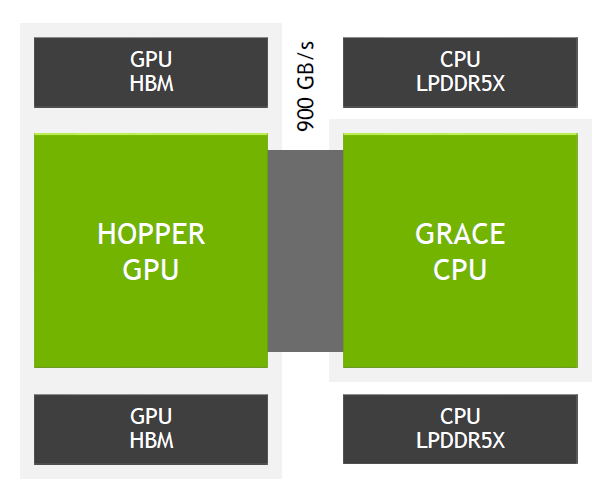

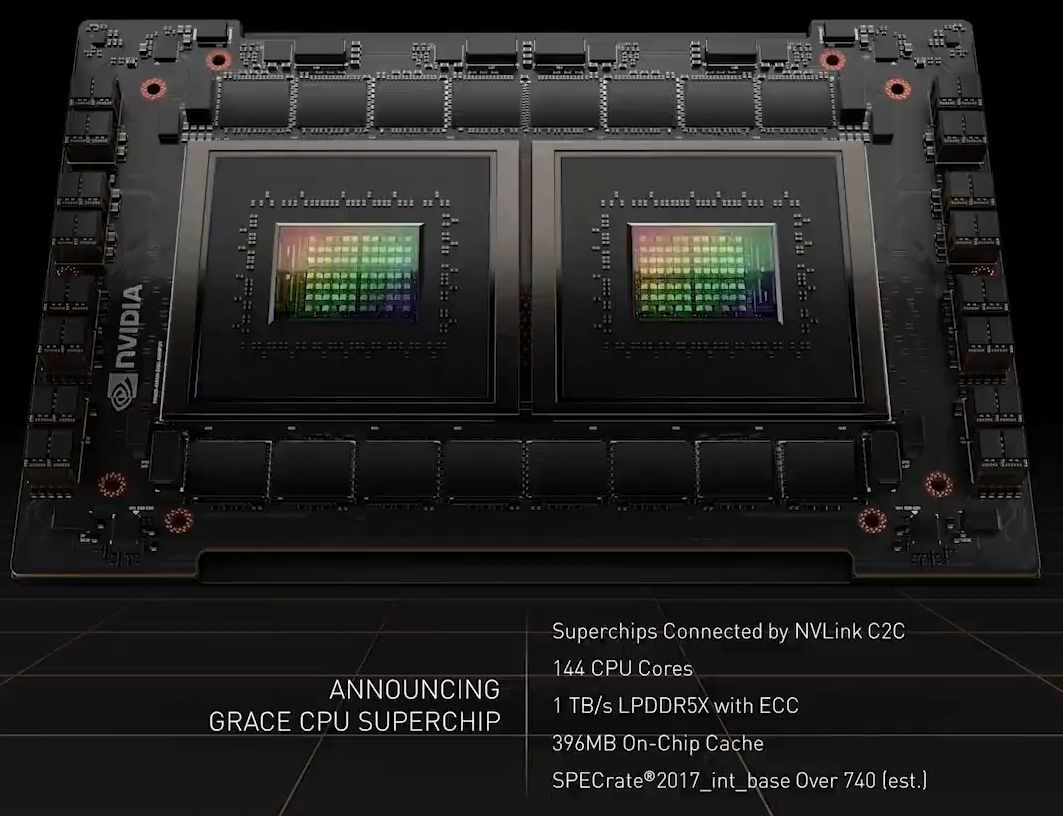

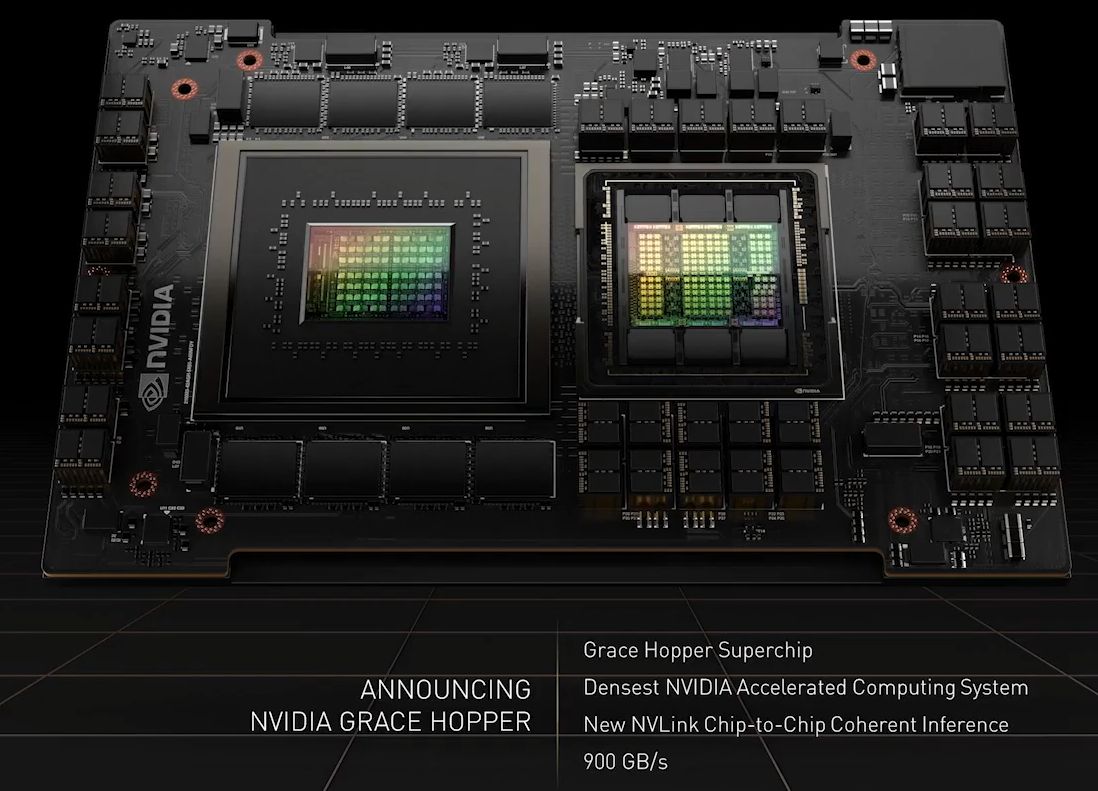

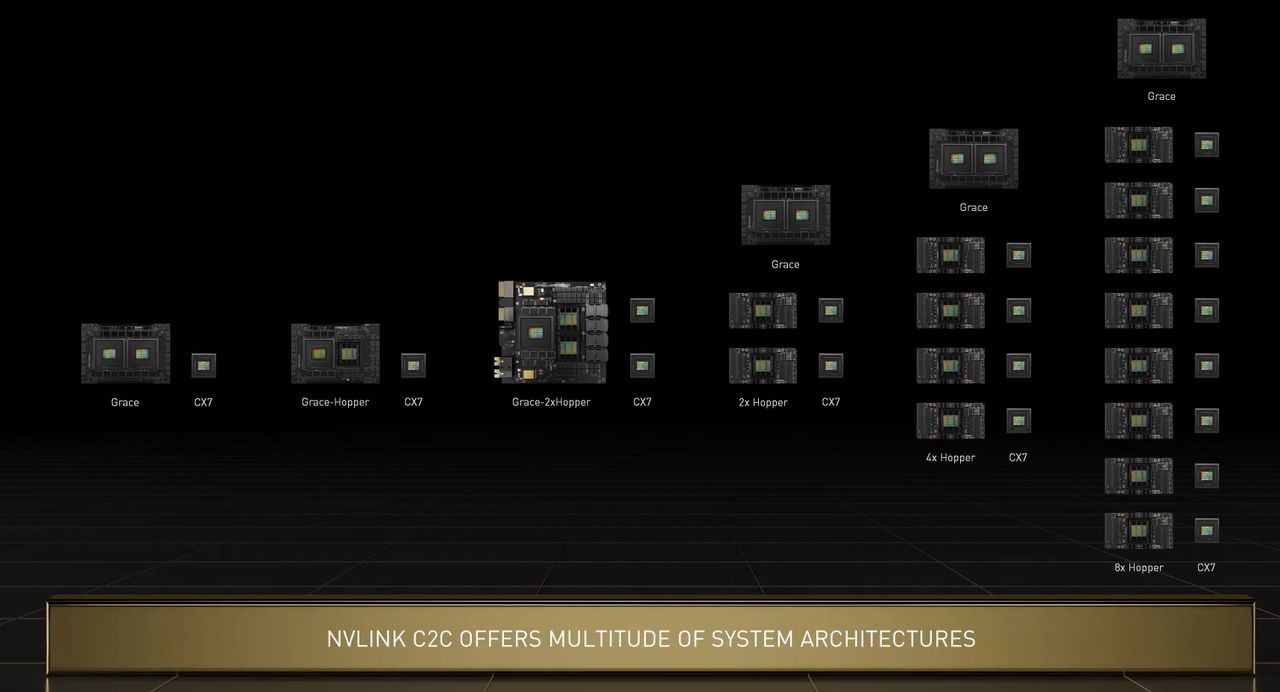

事實上,以實際產品而言,Nvidia將提供Grace CPU Superchip與Grace Hopper Superchip等兩種形式。在單一封裝當中,前者置入2個Grace CPU,搭配LPDDR5X記憶體,後者置入1個Grace GPU,搭配LPDDR5X記憶體,以及1個Hopper GPU,內建HBM記憶體;而在CPU與CPU之間,以及CPU與GPU之間的晶片互連介面,則是採用Nvidia發展的NVLink-C2C介面。

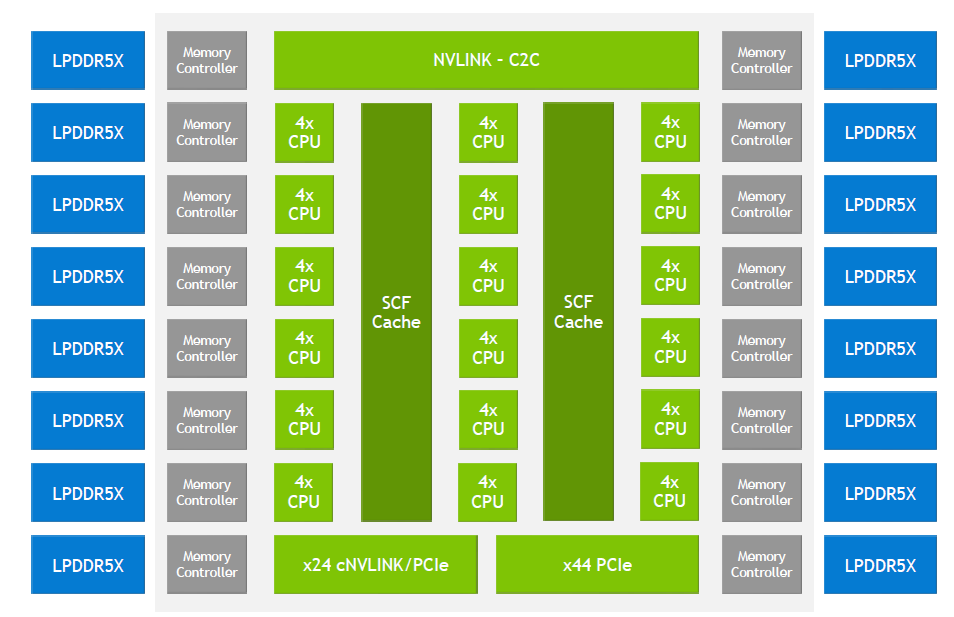

單就其中的Grace GPU晶片而言,導入台積電4N製程節點而成,內建72顆採用Arm Neoverse V2平臺的CPU核心,在DRAM記憶體容量、類型、存取方式、頻寬等配置上,最大可支援512 GB的LPDDR5X、32個記憶體通道,以及546 GB/s記憶體頻寬。而相關資訊公開之後,也讓我們進一步理解Nvdia去年4月與今年3月GTC大會揭露的名稱與規格,其實並不矛盾,彼此之間原來是有這樣的組合關係。

最初他們僅提到Grace CPU是Arm架構,可運用LPDDR5x記憶體,並且能結合系統記憶體與GPU的HBM高頻寬記憶體,形成單一記憶體定址空間,底層將採用頻寬為900 GB/s的第4代NVLink互連技術與GPU相接,預計在2023年初推出。

到了今年3月,他們突然提出Grace CPU Superchip與Grace Hopper Superchip,兩款晶片預計在2023年上半問世,而這樣的訊息可能讓很多人以為更改產品名稱與擴充陣容。Nvidia當時表示,Grace CPU Superchip是結合2個處理器晶片,並且搭配新的晶片互連介面 NVLink-C2C而成,單顆封裝內建144個Armv9架構的核心,記憶體頻寬為1 TB/s,而先前亮相的晶片,他們僅提到是CPU與GPU的整合模組Grace Hopper Superchip,未透露更多資訊。

等到8月底、9月中,Nvidia終於揭開Grace神祕面紗,再加上Arm發表Neoverse V2平臺,各界對於Grace處理器的三種形態,以及Arm新平臺的助益,也有了進一步瞭解。

熱門新聞

2026-02-11

2026-02-11

2026-02-12

2026-02-09

2026-02-10

2026-02-10

2026-02-06